# IBM eserver pSeries 670 and pSeries 690 System Handbook

Redbooks

# IBM

# International Technical Support Organization

IBM @server pSeries 670 and pSeries 690 System Handbook

May 2003

Note: Before using this information and the product it supports, read the information in "Notices" on page xiii. Third Edition (May 2003) This edition applies to IBM @server pSeries 670 Model 671 and IBM @server pSeries 690 for use with the AIX 5L Version 5.1 (program number 5765-E61) and AIX 5L Version 5.2 (program number 5765-E62).

© Copyright International Business Machines Corporation 2002, 2003. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule

this redbook for more current information.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

**Note:** This book is based on a pre-GA version of product IBM Hardware Management Console for pSeries software Release 3.2 and may not apply when the product becomes generally available. We recommend that you consult the product documentation or follow-on versions of

# **Contents**

| Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Notices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Preface       x         The team that wrote this redbook       x         Become a published author       x         Comments welcome       x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Summary of changesxApril 2003, Third EditionxOctober 2002, Second EditionxMarch 2002, First Editionx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 1. Overview of the pSeries 670 and pSeries 690  1.1 What's new in the pSeries 670 and pSeries 690.  1.2 pSeries 670 and pSeries 690 characteristics  1.2.1 Microprocessor technology  1.2.2 Memory subsystem  1.2.3 I/O drawer subsystem  1.2.4 Hardware technology  1.3 Logical partitioning  1.4 Dynamic logical partitioning.  1.5 General overview of pSeries 670 and pSeries 690.  1.6 Market positioning  1.7 Supported operating systems  1.7.1 AIX 5L Version 5.1  1.7.2 AIX 5L Version 5.2  1.7.3 Linux - SuSE  1.7.4 Comparison of RAS supported features  1.7.5 Installation and backup of the operating systems |

| Chapter 2. Hardware architecture of the pSeries 670 and pSeries 690                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.3.1 POWER4 processor and MCM packaging                                                                                | 22  |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| 2.3.2 Memory subsystem for pSeries 690                                                                                  | 29  |

| 2.3.3 MCMs and GX slots relationship for pSeries 690                                                                    |     |

| 2.3.4 Memory subsystem for pSeries 670                                                                                  | 42  |

| 2.3.5 MCMs and GX slots relationship for pSeries 670                                                                    |     |

| 2.3.6 I/O books                                                                                                         | 47  |

| 2.3.7 Service processor                                                                                                 | 50  |

| 2.4 I/O subsystem                                                                                                       | 51  |

| 2.4.1 I/O drawer                                                                                                        | 51  |

| 2.4.2 I/O subsystem communication and monitoring                                                                        | 56  |

| 2.4.3 I/O drawer physical placement order                                                                               | 65  |

| 2.4.4 Media drawer                                                                                                      | 70  |

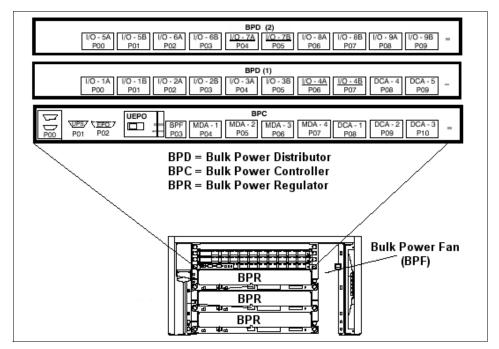

| 2.5 Power subsystem                                                                                                     | 72  |

| 2.5.1 Bulk power assembly                                                                                               | 73  |

| 2.5.2 Internal battery feature                                                                                          | 74  |

| 2.5.3 Cooling                                                                                                           |     |

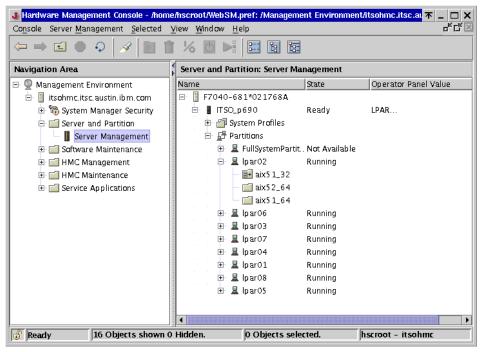

| 2.6 IBM Hardware Management Console for pSeries                                                                         | 75  |

|                                                                                                                         |     |

| Chapter 3. Using the IBM Configurator for e-business                                                                    | 79  |

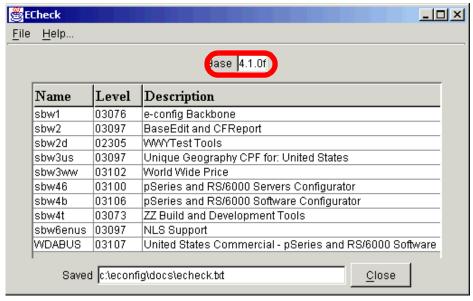

| 3.1 What's new with e-config.                                                                                           |     |

| 3.2 Configuration rules for pSeries 670 and pSeries 690                                                                 |     |

| 3.2.1 Minimum configuration for the pSeries 670 and pSeries 690.                                                        |     |

| 3.2.2 LPAR considerations.                                                                                              |     |

| 3.2.3 Processor configuration rules                                                                                     |     |

| 3.2.4 Memory configuration rules                                                                                        |     |

| 3.2.5 I/O books                                                                                                         |     |

| 3.2.6 Media drawer configuration rules                                                                                  |     |

| 3.2.7 I/O drawer configuration rules                                                                                    |     |

| 3.2.8 I/O loops and cabling                                                                                             |     |

| 3.2.9 Graphics console configuration rules                                                                              |     |

| 3.2.10 Rack and power units configuration rules                                                                         |     |

| 3.2.11 HMC configuration rules                                                                                          |     |

| 3.2.12 SP Cluster 1600 considerations                                                                                   |     |

| 3.2.13 Upgrade considerations                                                                                           |     |

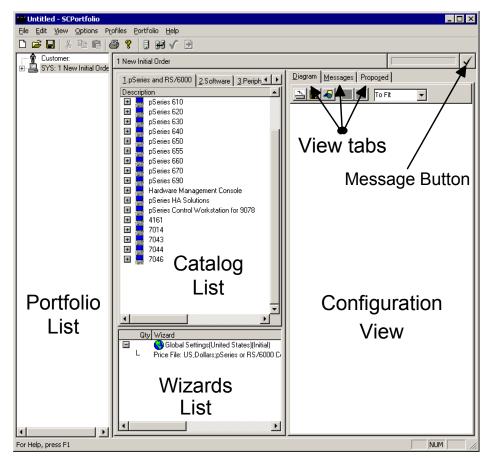

| 3.3.1 Initial order                                                                                                     |     |

|                                                                                                                         |     |

| 3.3.2 Performing an upgrade                                                                                             |     |

| 3.4 Configuration examples                                                                                              |     |

| 3.4.1 Configuration example 1: pSeries 670 (16-way 1.1 GHz) 3.4.2 Configuration example 2: pSeries 690 (24-way 1.3 GHz) |     |

| 3.4.2 Configuration example 2: pSeries 690 (24-way 1.3 GHz) 3.4.3 Model conversion from pSeries 670 to pSeries 690      |     |

| 3.4.4 Feature conversion from POWER4 to POWER4+                                                                         |     |

| 3.4.4 realure conversion from POWER4 to POWER4+                                                                         | 12/ |

| Chapter 4. Capacity Upgrade on Demand                        |       |

|--------------------------------------------------------------|-------|

| 4.1 What's new in CUoD                                       | 134   |

| 4.2 Description of CUoD                                      | . 134 |

| 4.2.1 Trial CoD function                                     | . 135 |

| 4.2.2 Overview of CUoD configurations                        | 136   |

| 4.2.3 Supported CUoD Processor configurations                | . 138 |

| 4.2.4 Supported CUoD Memory configurations                   | . 141 |

| 4.2.5 CUoD resource sequencing                               | 142   |

| 4.2.6 Logical and physical entities                          | 143   |

| 4.2.7 CUoD license screen                                    | 144   |

| 4.2.8 CUoD error messages                                    | . 145 |

| 4.3 Activating CUoD resources                                | 146   |

| 4.3.1 CUoD resources activation and order process            | . 147 |

| 4.3.2 Trial CoD processor and memory                         |       |

| 4.4 Dynamic Processor Sparing                                |       |

| 4.5 On/Off Capacity on Demand                                |       |

|                                                              |       |

| Chapter 5. Reliability, availability, and serviceability     |       |

| 5.1 What's new in serviceability                             |       |

| 5.2 RAS features                                             |       |

| 5.3 Predictive functions                                     |       |

| 5.3.1 Service processor                                      |       |

| 5.3.2 First Failure Data Capture (FFDC)                      |       |

| 5.3.3 Predictive failure analysis                            |       |

| 5.3.4 Component reliability                                  |       |

| 5.3.5 Extended system testing and surveillance               |       |

| 5.4 Redundancy in components                                 |       |

| 5.4.1 Power and cooling                                      |       |

| 5.4.2 Memory redundancy mechanisms                           |       |

| 5.4.3 Multiple data paths                                    |       |

| 5.5 Fault recovery                                           |       |

| 5.5.1 PCI bus parity error recovery and PCI bus deallocation | 166   |

| 5.5.2 Dynamic CPU deallocation                               | 168   |

| 5.5.3 CPU Guard                                              | 168   |

| 5.5.4 Caches and memory deallocation                         | . 172 |

| 5.5.5 Hot-swappable components                               | 172   |

| 5.5.6 Hot-swappable boot disks                               | 174   |

| 5.5.7 Hot-Plug PCI adapters                                  | 174   |

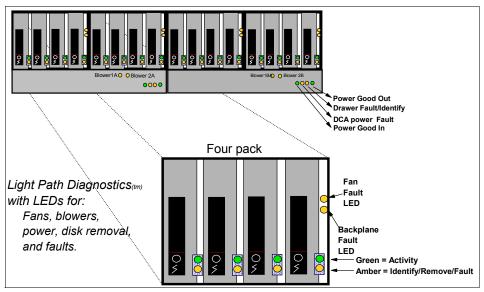

| 5.5.8 Light Path Diagnostics                                 | 176   |

| 5.6 Serviceability features                                  | . 177 |

| 5.6.1 Back up of HMC                                         |       |

| 5.6.2 Upgrading HMC                                          | 181   |

| 5.6.3 Microcode Updates function                             | . 184 |

| 5.6.4 Inventory Scout Services                         |     |

|--------------------------------------------------------|-----|

| 5.6.5 Service Agent                                    |     |

| 5.6.7 Problem determination hints of Service Functions |     |

| 5.7 AIX RAS features                                   |     |

| 5.7.1 Unrecoverable error analysis                     |     |

| 5.7.2 System hang detection                            |     |

| 5.7.3 AIX disk mirroring and LVM sparing               |     |

| 5.7.4 TCP/IP RAS enhancements                          | 208 |

| Appendix A. Minimum and default configurations         |     |

| A.2 pSeries 690 configurations                         | 212 |

| Appendix B. I/O loop cabling and performance           | 217 |

| Abbreviations and acronyms                             | 227 |

| Related publications                                   | 231 |

| IBM Redbooks                                           |     |

| Other publications                                     | 231 |

| Online resources                                       |     |

| How to get IBM Redbooks                                | 234 |

|                                                        |     |

# **Figures**

| 1-1  | The IBM @server pSeries 690                                   | 6   |

|------|---------------------------------------------------------------|-----|

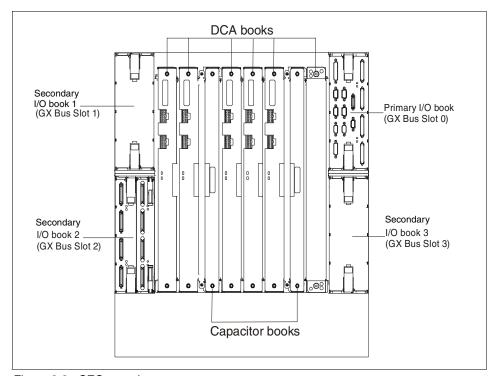

| 2-1  | The pSeries 670 and pSeries 690 base rack with components     | 19  |

| 2-2  | CEC front view                                                | 20  |

| 2-3  | CEC rear view                                                 | 21  |

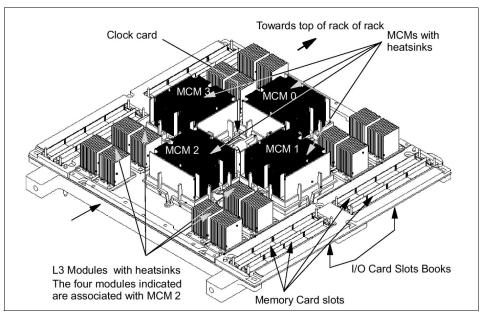

| 2-4  | CEC backplane orthogonal view                                 | 22  |

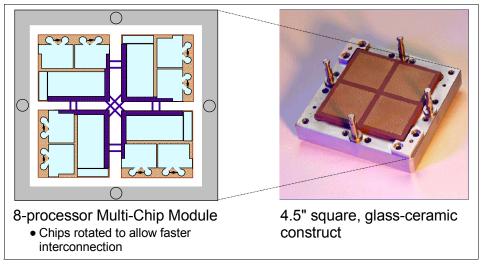

| 2-5  | POWER4 multichip module                                       | 26  |

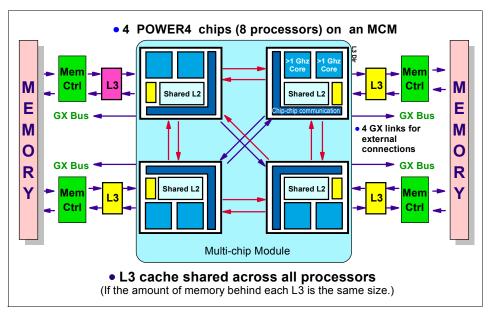

| 2-6  | Multichip module with L2, L3, and memory                      | 27  |

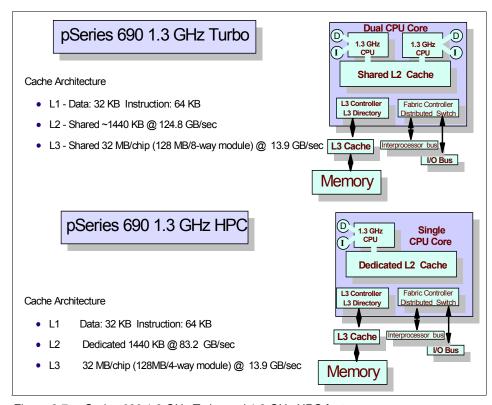

| 2-7  | pSeries 690 1.3 GHz Turbo and 1.3 GHz HPC feature             | 29  |

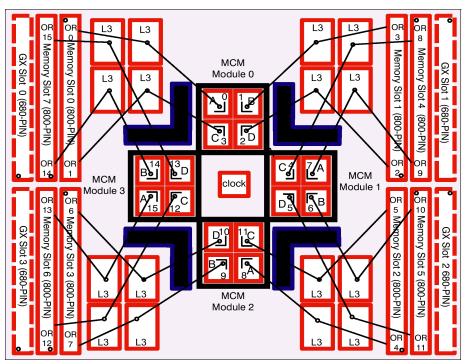

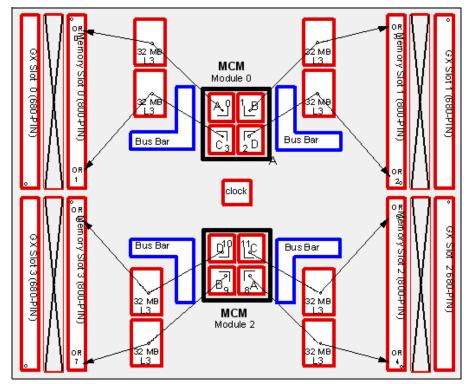

| 2-8  | MCM, L3 cache, and memory slots relationship on backplane     | 30  |

| 2-9  | Logical relationship between MCMs, memory, and GX Slots       | 31  |

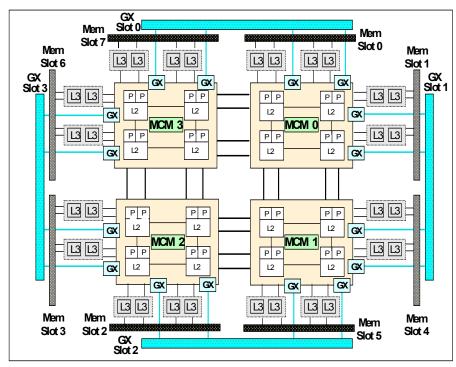

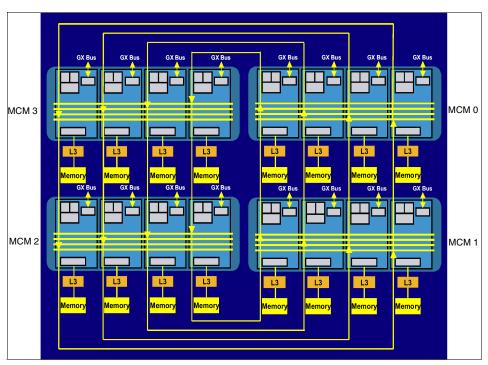

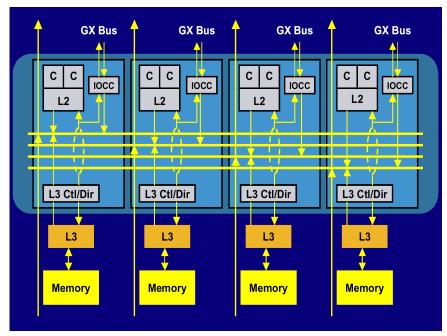

| 2-10 | Interconnection between four MCMs                             | 32  |

| 2-11 | Interconnection between processors in an MCM                  | 33  |

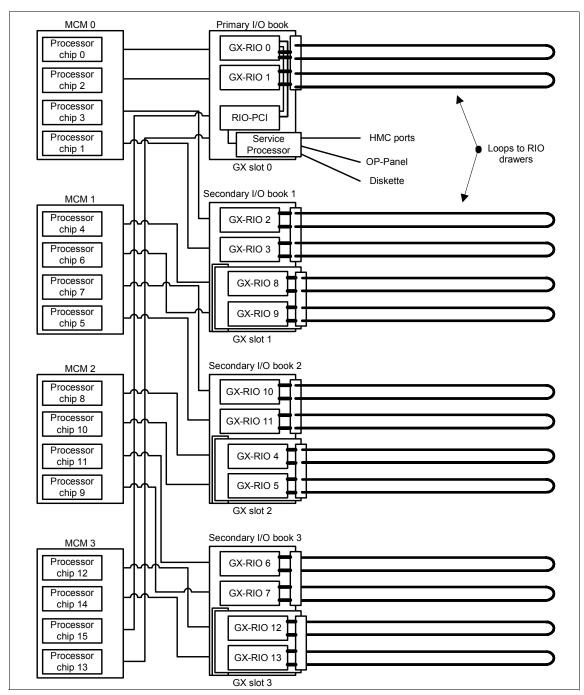

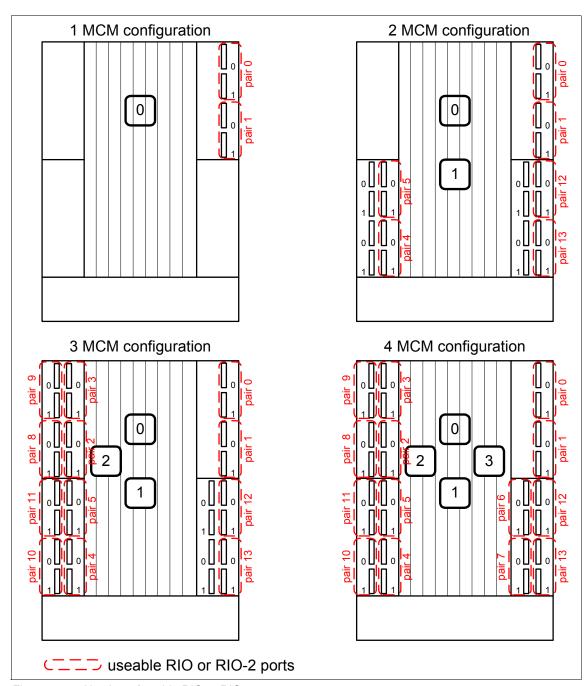

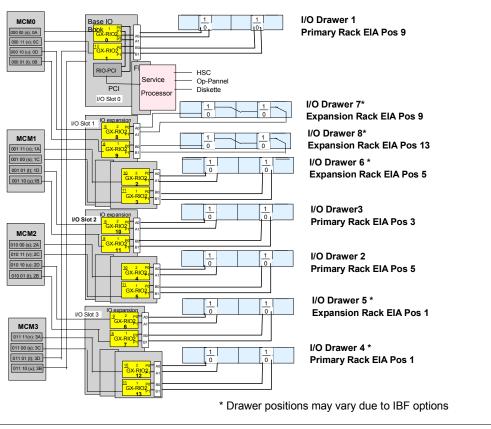

| 2-12 | MCMs and RIO ports relationship (pSeries 690)                 | 41  |

| 2-13 | MCM, L3 cache, and memory slots relationship on backplane     | 43  |

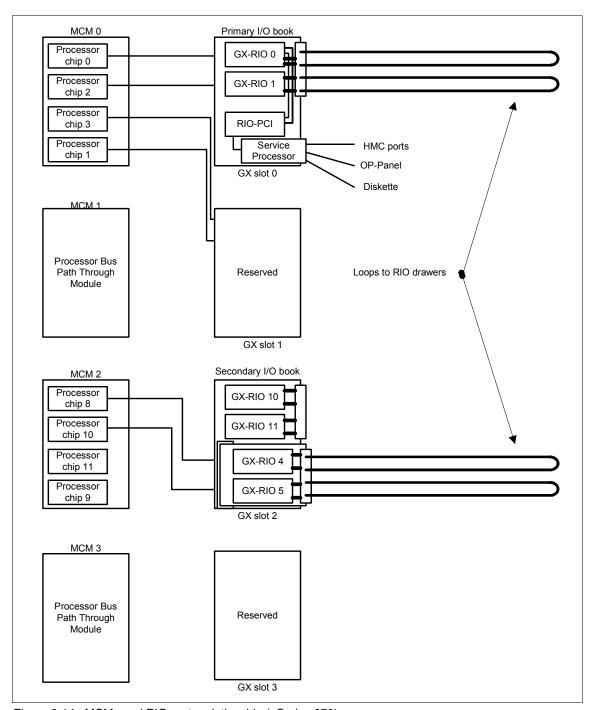

| 2-14 | MCMs and RIO ports relationship (pSeries 670)                 |     |

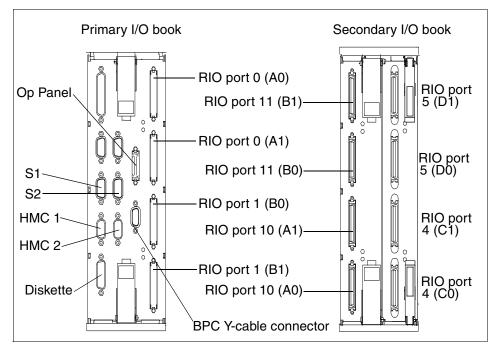

| 2-15 | Primary and secondary I/O books                               | 48  |

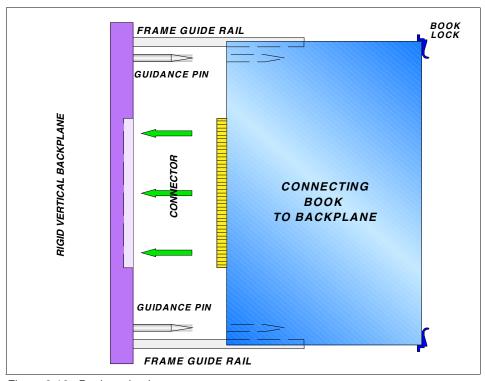

| 2-16 | Book packaging                                                | 50  |

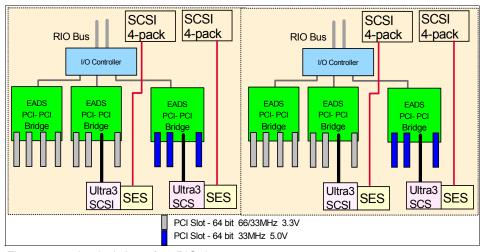

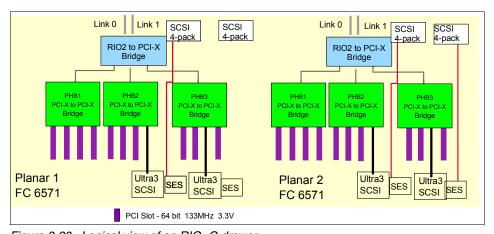

| 2-17 | I/O drawer rear view                                          |     |

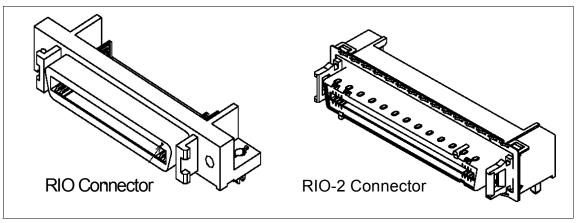

| 2-18 | Difference between RIO and RIO-2 connectors                   |     |

| 2-19 | Logical view of an RIO drawer                                 |     |

| 2-20 | Logical view of an RIO -G drawer                              |     |

| 2-21 | RIO loops supported configurations                            |     |

| 2-22 | RIO-2 loops supported configurations                          |     |

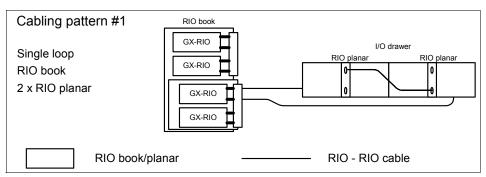

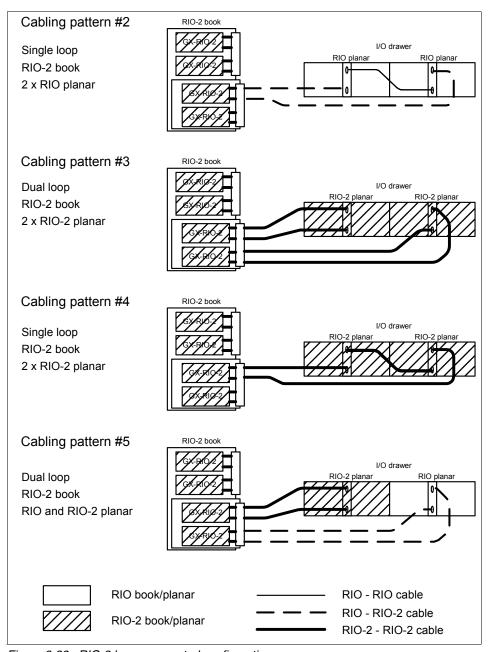

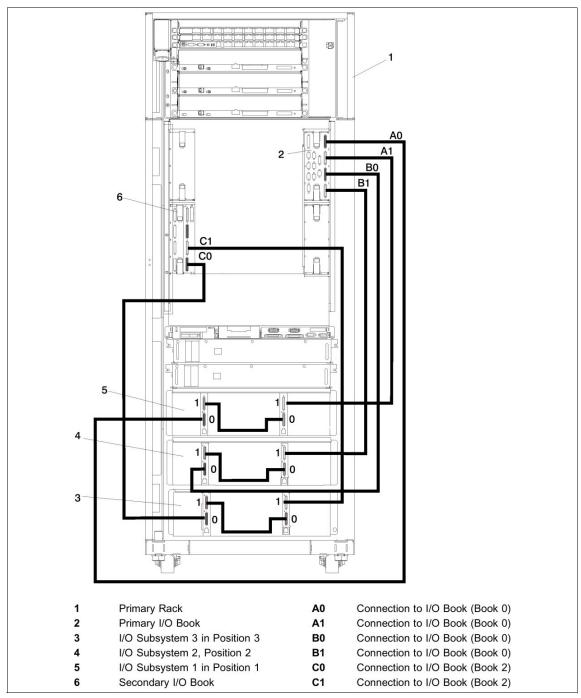

| 2-23 | RIO connections for three I/O drawers with IBF configuration  |     |

| 2-24 | Number of usable RIO or RIO-2 ports                           |     |

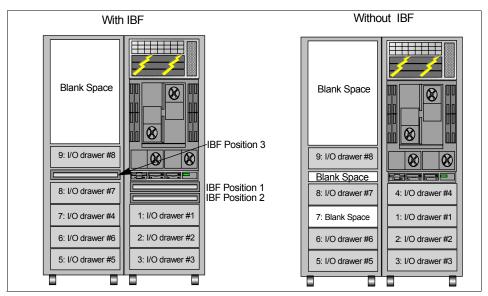

| 2-25 | I/O drawer and IBF placement positions (pSeries 690)          |     |

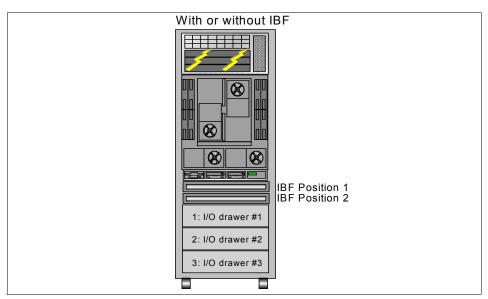

| 2-26 | I/O drawer and IBF placement positions (pSeries 670)          |     |

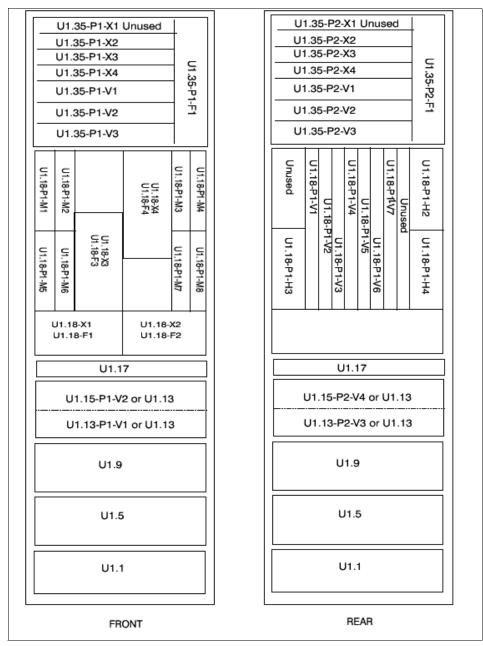

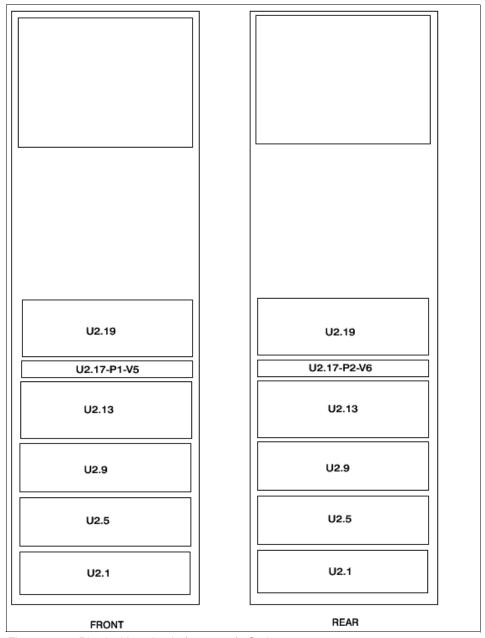

| 2-27 | Physical location in frame 1 of pSeries 670 and pSeries 690   |     |

| 2-28 | Physical location in frame 2 of pSeries 690                   |     |

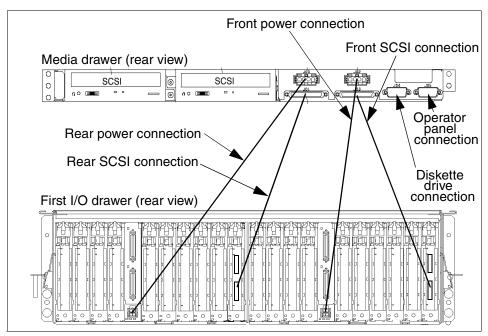

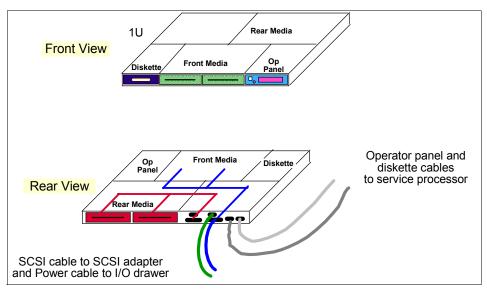

| 2-29 | Media drawer power and SCSI connection                        |     |

| 2-30 | Media drawer                                                  |     |

| 2-31 | Power subsystem locations in BPA                              |     |

| 2-32 | Graphical user interface on the HMC                           |     |

| 3-1  | IBM Configurator for e-business <i>version</i>                |     |

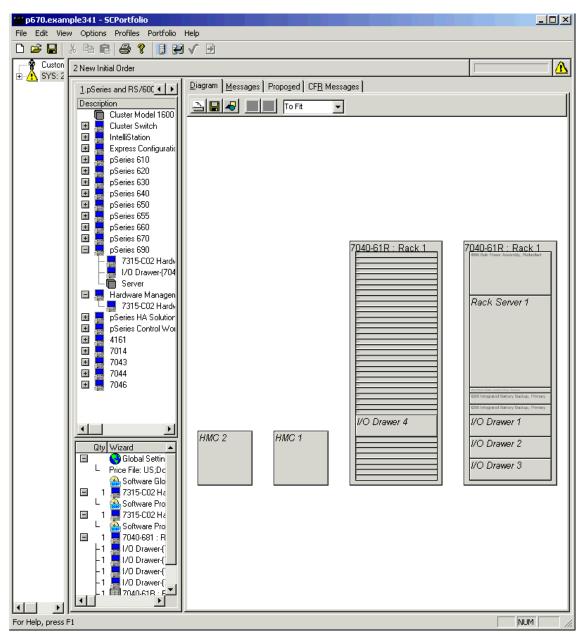

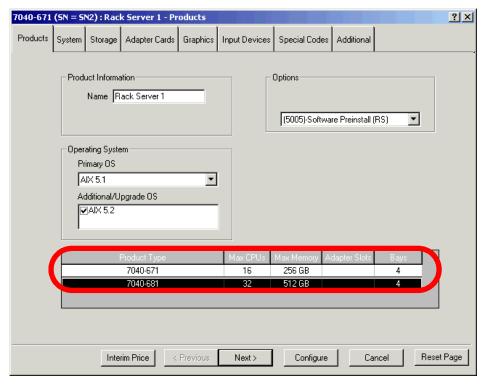

| 3-2  | Add Initial Order icon                                        |     |

| 3-3  | The e-config main panel                                       |     |

| 3-4  | Graphical representation of pSeries 690 in configuration view |     |

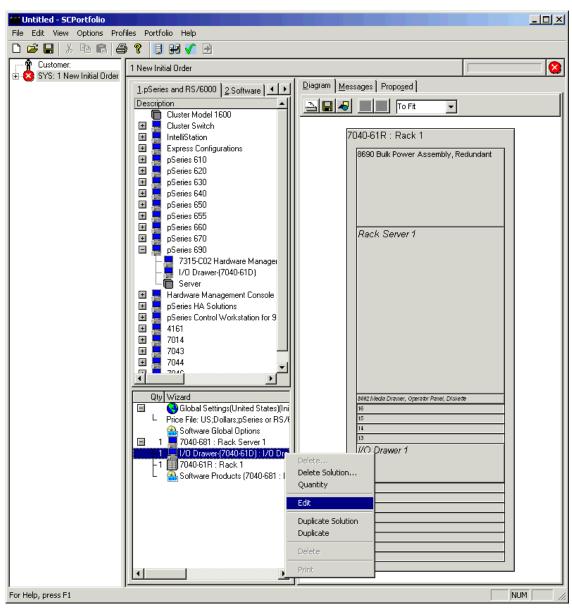

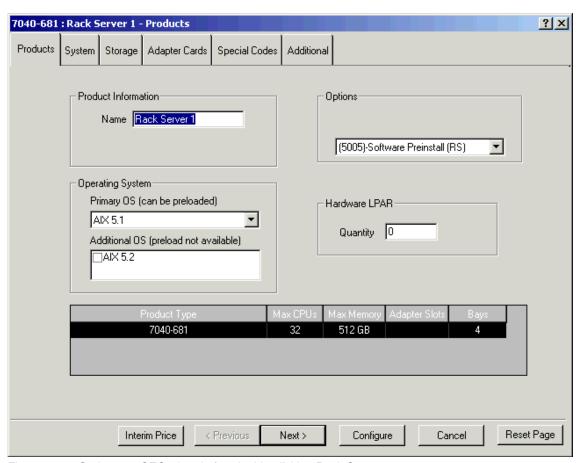

| 3-5  | pSeries 690 CEC wizard after double-clicking Rack Server 1    | 101 |

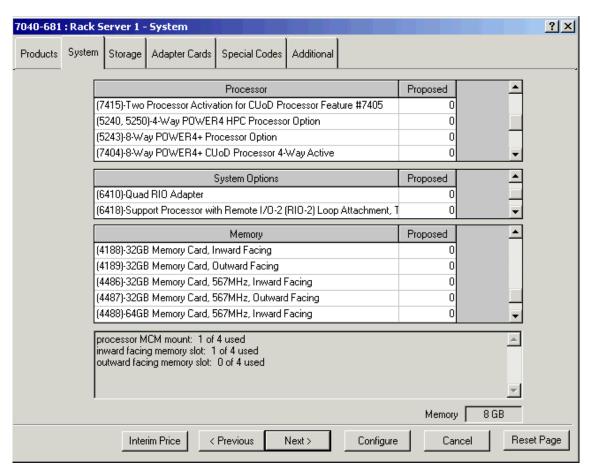

| 3-6  | System tab for the pSeries 690                                  | 103 |

|------|-----------------------------------------------------------------|-----|

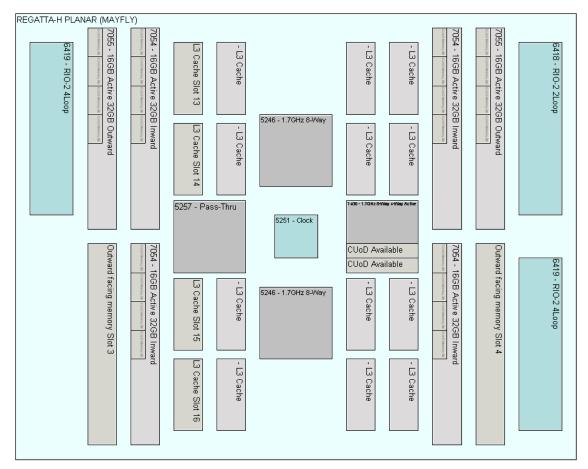

| 3-7  | Detailed diagram for the pSeries 690 CEC                        | 105 |

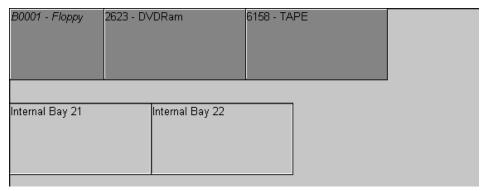

| 3-8  | Detailed diagram for the media drawer                           | 106 |

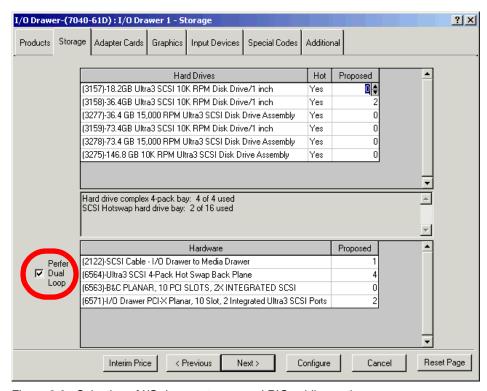

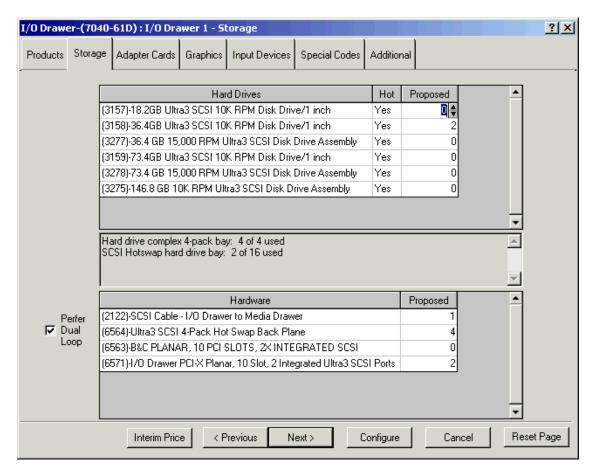

| 3-9  | Selection of I/O drawer storage and RIO cabling options         | 107 |

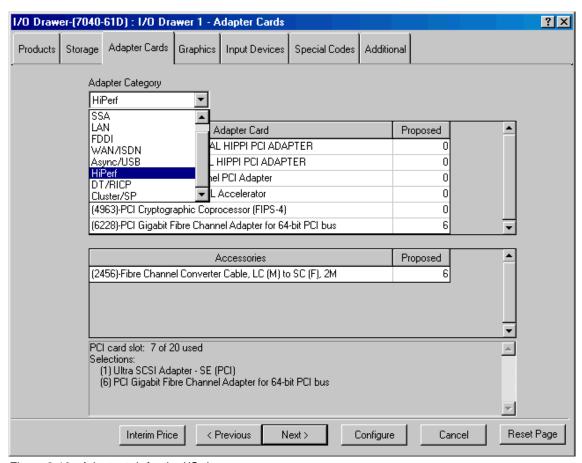

| 3-10 | Adapter tab for the I/O drawer                                  | 108 |

| 3-11 | Adapter tab with LAN adapter category selected                  | 109 |

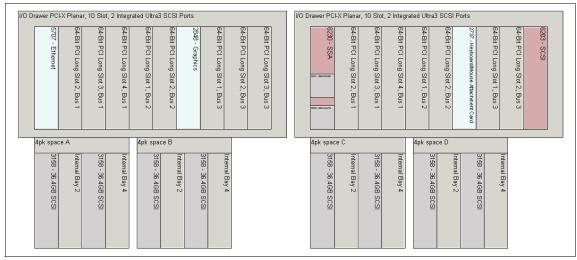

| 3-12 | Detailed diagram of the I/O drawer                              | 110 |

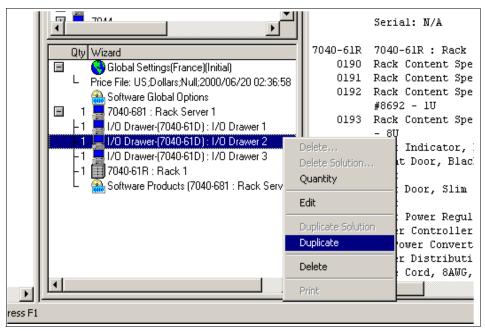

| 3-13 | Duplicating an existing drawer                                  | 111 |

| 3-14 | Selecting a new I/O drawer                                      | 111 |

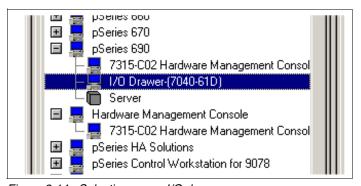

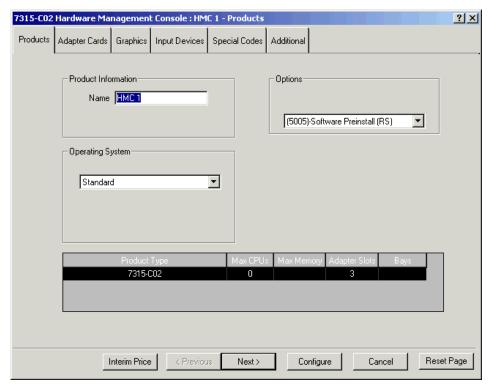

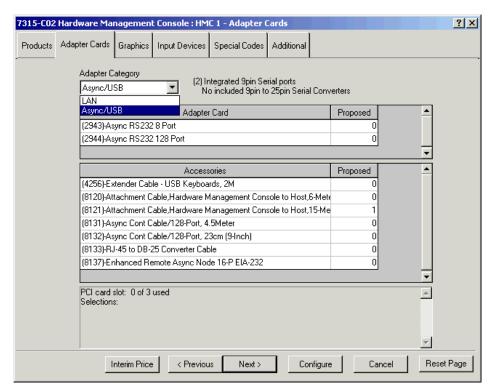

| 3-15 | HMC wizard                                                      |     |

| 3-16 | HMC adapter options                                             |     |

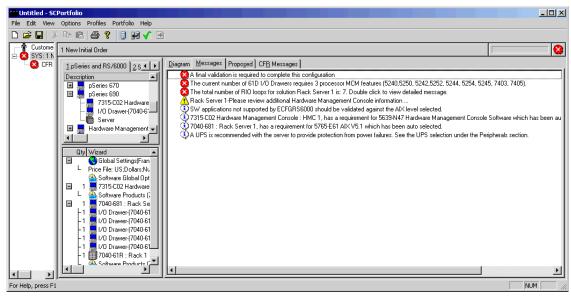

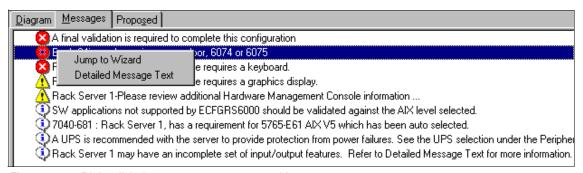

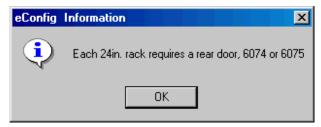

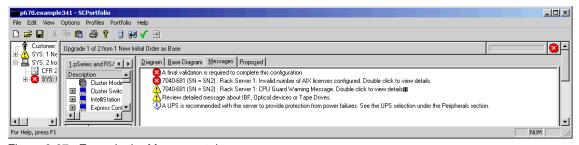

| 3-17 | The error, warning, and information output of the configuration | 115 |

| 3-18 | Right-click the error message text and it opens a menu          | 115 |

| 3-19 | Detailed error message                                          |     |

| 3-20 | Perform Final Validation icon                                   |     |

| 3-21 | Add Upgrade/MES or Restore CFR icon                             | 117 |

| 3-22 | Perform Final Validation icon                                   |     |

| 3-23 | A graphical representation of the final configuration           |     |

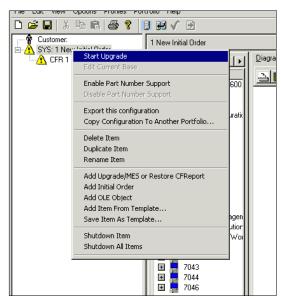

| 3-24 | Starting to upgrade an existing configuration                   |     |

| 3-25 | Start upgrading the CEC                                         |     |

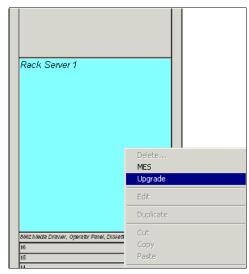

| 3-26 | Changing model to pSeries 690                                   |     |

| 3-27 | Errors in the Messages tab                                      |     |

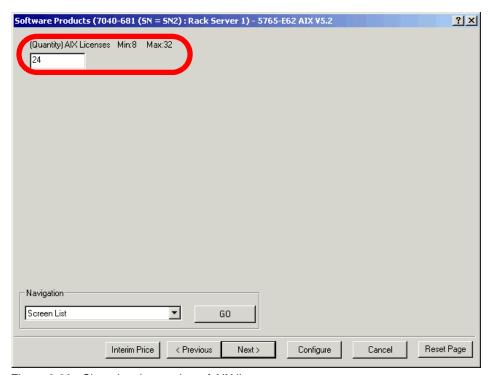

| 3-28 | Changing the number of AIX licenses                             |     |

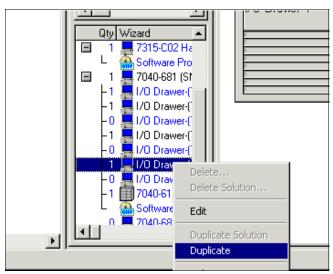

| 3-29 | Duplicating I/O drawer 4                                        |     |

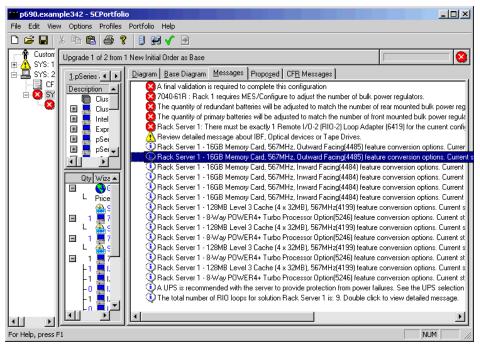

| 3-30 | Messages view during feature upgrade                            |     |

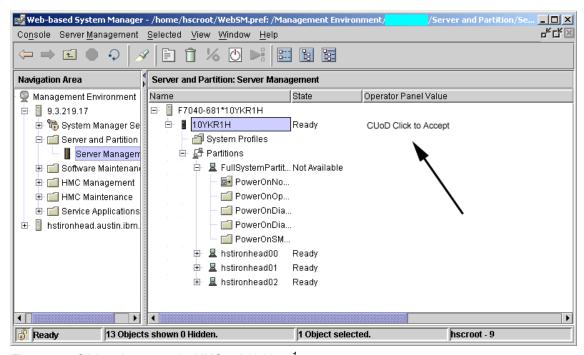

| 4-1  | Click to Accept on the HMC at initial boot                      |     |

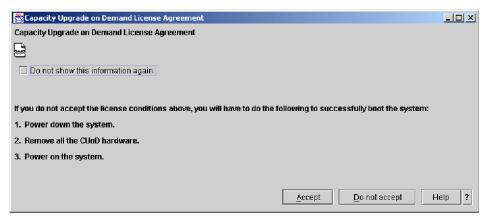

| 4-2  | Click to Accept window                                          |     |

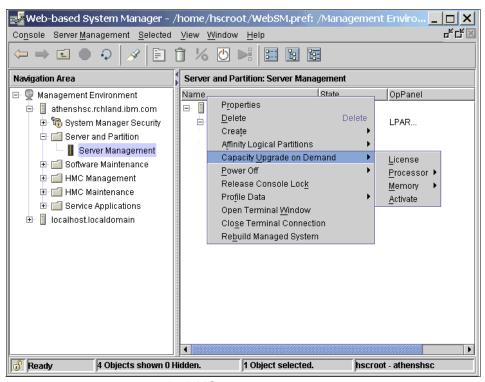

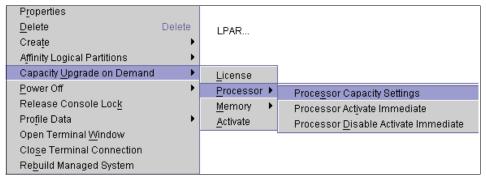

| 4-3  | CUoD menu on the HMC                                            |     |

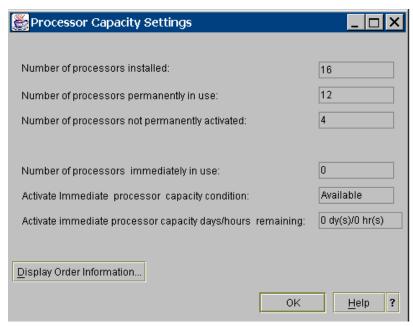

| 4-4  | Processor Capacity Settings                                     |     |

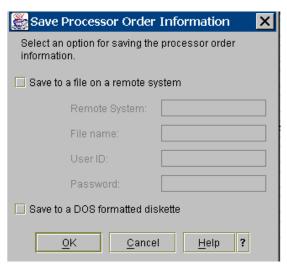

| 4-5  | Save Processor Order Information                                |     |

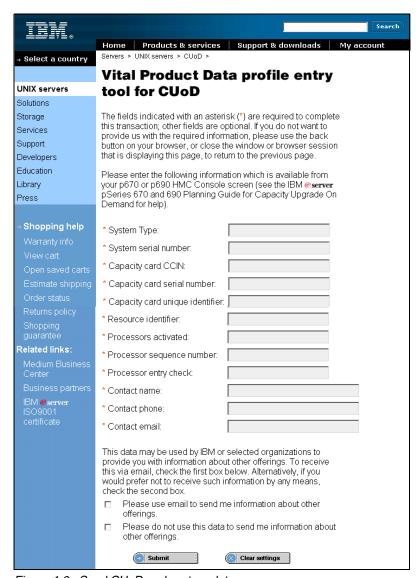

| 4-6  | Send CUoD and system data                                       |     |

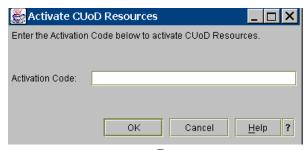

| 4-7  | Activate CUoD Resources                                         |     |

| 4-8  | To activate the resources using Trial CoD function              |     |

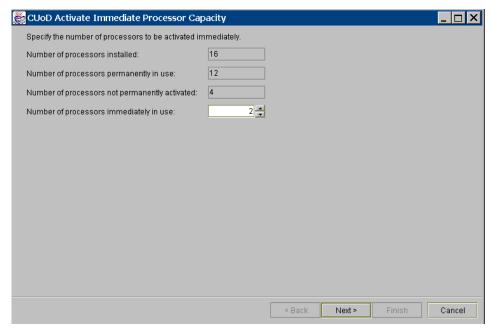

| 4-9  | CUoD Trial CoD Processor Capacity (Next) screen                 |     |

| 4-10 | CUoD Trial CoD Processor capacity (Finish) screen               |     |

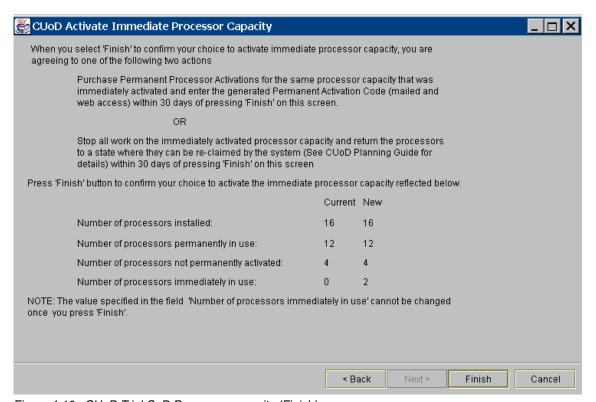

| 4-11 | Warning message to Disable Processor Trial CoD Capacity         |     |

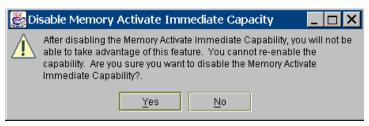

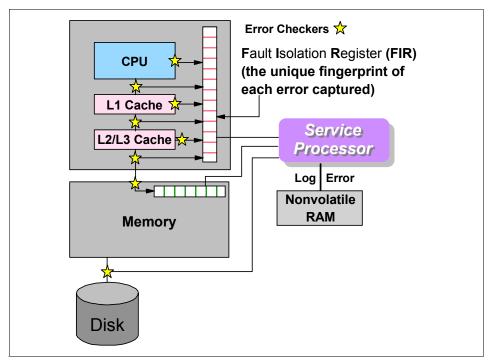

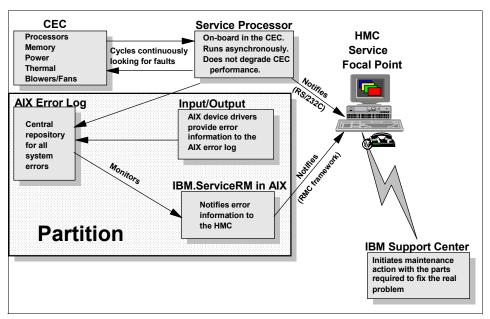

| 5-1  | Service processor schematic                                     |     |

| 5-2  | FFDC error checkers and fault isolation registers               |     |

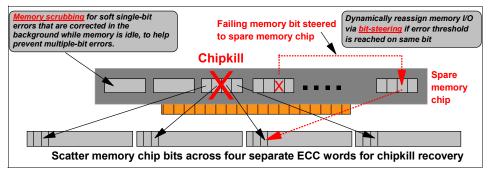

| 5-3  | Memory error recovery mechanisms                                |     |

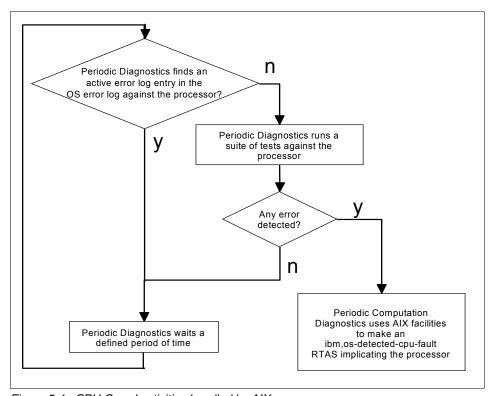

| 5-4  | CPU Guard activities handled by AIX                             |     |

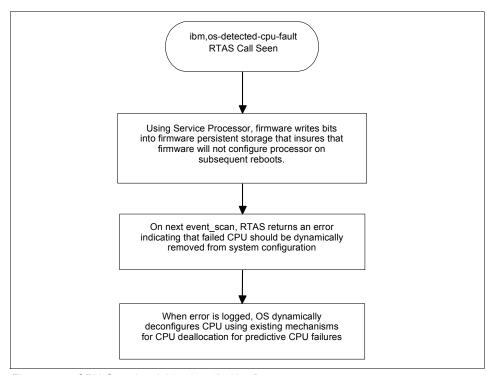

| 5-5  | CPU Guard activities handled by firmware                        |     |

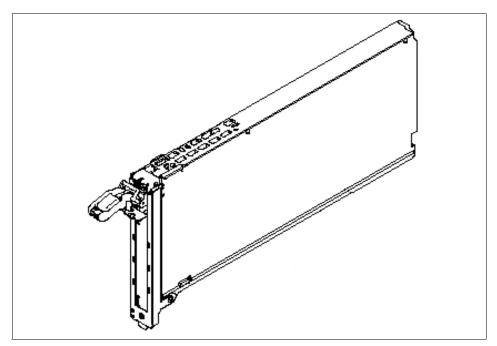

| 5-6  | Blind swap cassette                                             |     |

| 5-7  | Hot-Plug PCI adapters, blind swap cassette, and status LEDs     | 176 |

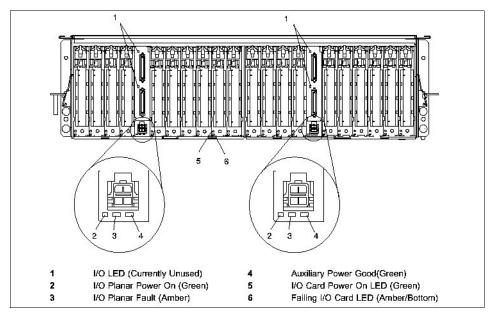

| 5-8  | Status LEDs for components in I/O drawers                      | 177 |

|------|----------------------------------------------------------------|-----|

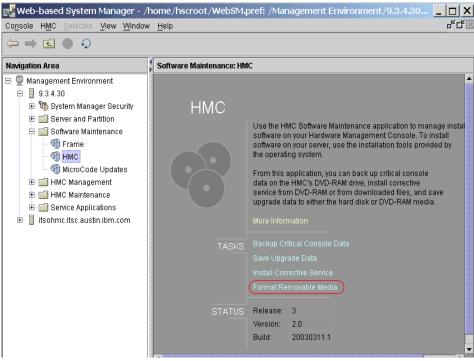

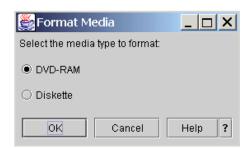

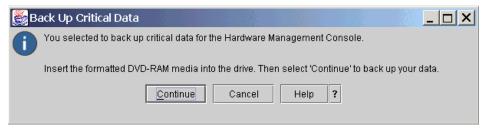

| 5-9  | Software maintenance                                           | 178 |

| 5-10 | Service Applications                                           | 179 |

| 5-11 | Error reporting and consolidation                              | 180 |

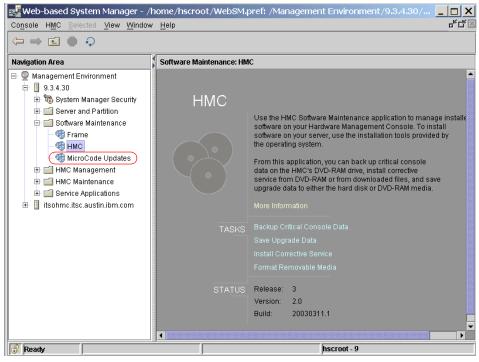

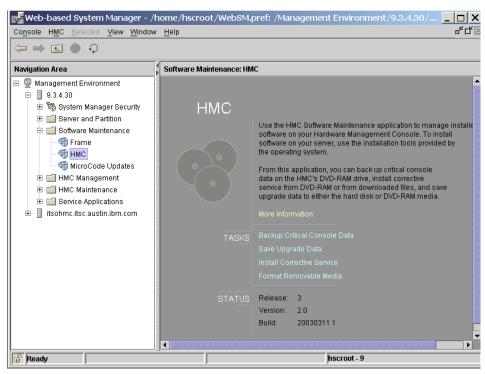

| 5-12 | Software Maintenance: HMC                                      | 182 |

| 5-13 | Format Media                                                   | 182 |

| 5-14 | Backup Critical Data                                           | 183 |

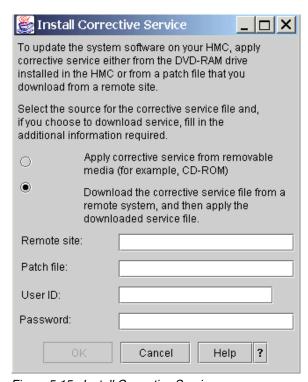

| 5-15 | Install Corrective Service                                     | 183 |

| 5-16 | Software Maintenance: HMC (2)                                  | 184 |

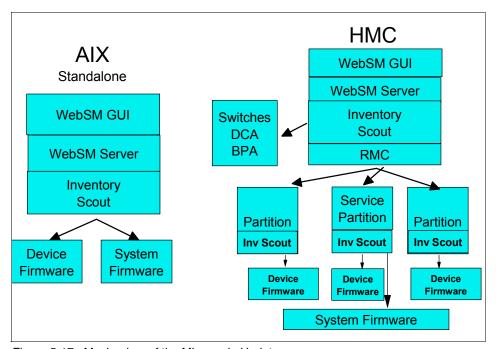

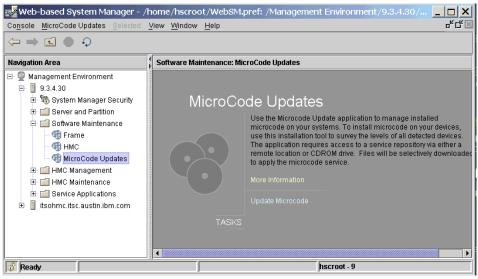

| 5-17 | Mechanism of the Microcode Updates                             | 185 |

| 5-18 | Microcode Updates                                              | 186 |

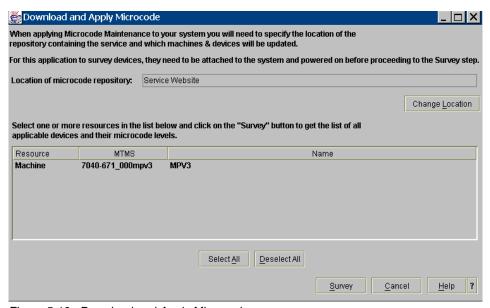

| 5-19 | Download and Apply Microcode                                   | 186 |

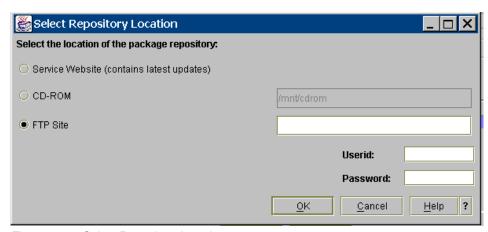

| 5-20 | Select Repository Location                                     |     |

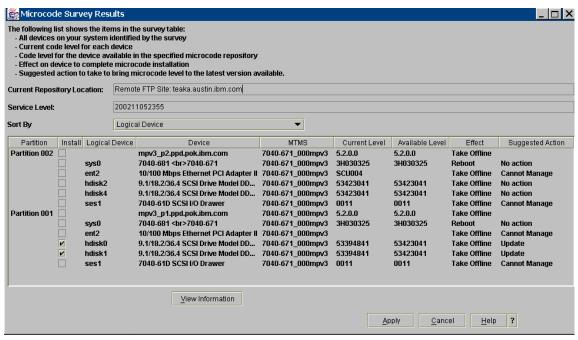

| 5-21 | Microcode Survey Results                                       | 188 |

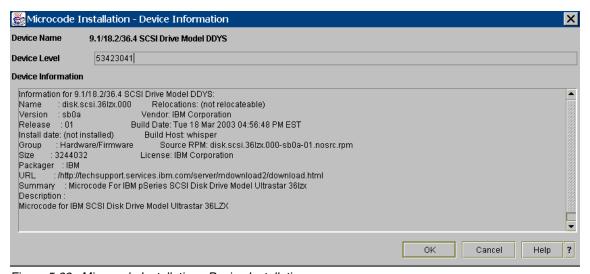

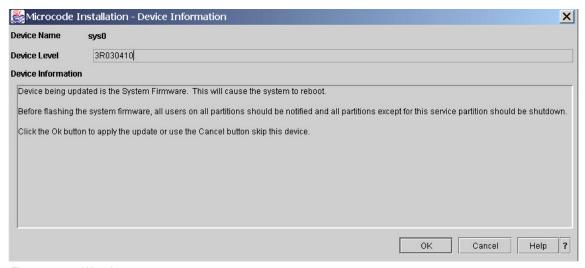

| 5-22 | Microcode Installation - Device Installation                   | 188 |

| 5-23 | Warning message                                                | 189 |

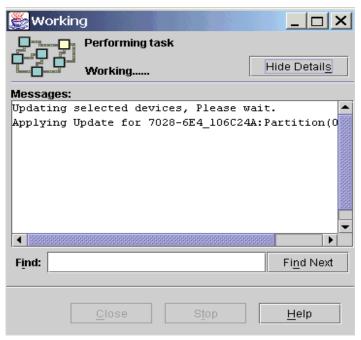

| 5-24 | Updating microcodes                                            | 190 |

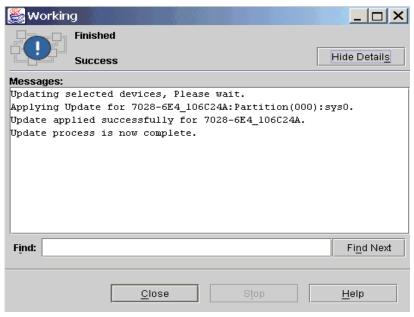

| 5-25 | Microcode Updates completed                                    | 191 |

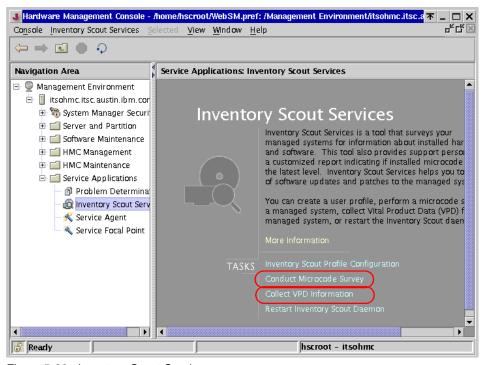

| 5-26 | Inventory Scout Services                                       | 192 |

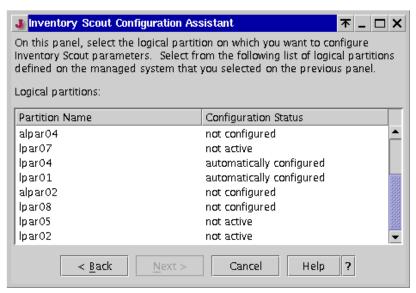

| 5-27 | Inventory Scout Configuration Assistant                        | 195 |

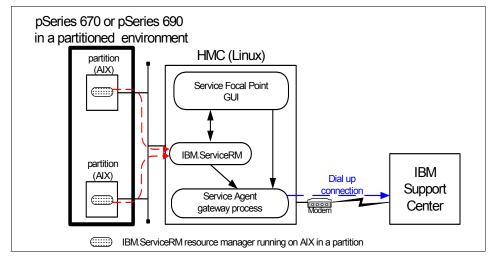

| 5-28 | Service Agent on the HMC                                       | 196 |

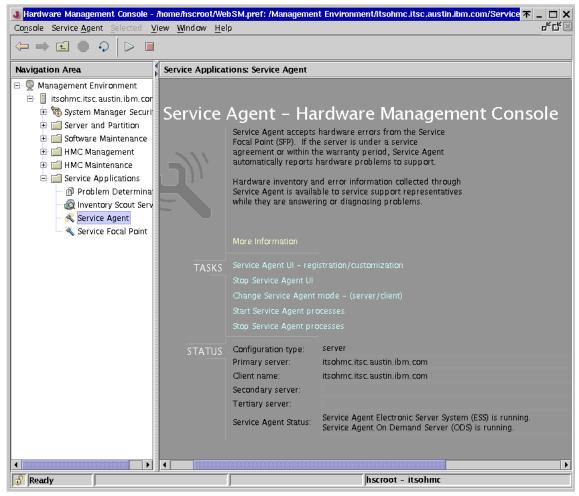

| 5-29 | Service Agent on the HMC                                       | 197 |

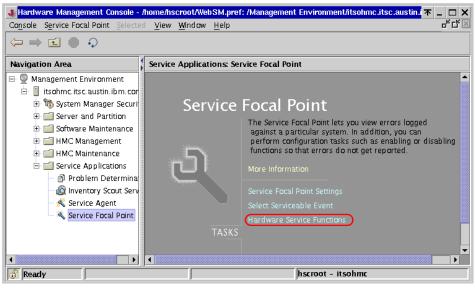

| 5-30 | Service Focal Point: Hardware Service Functions                | 199 |

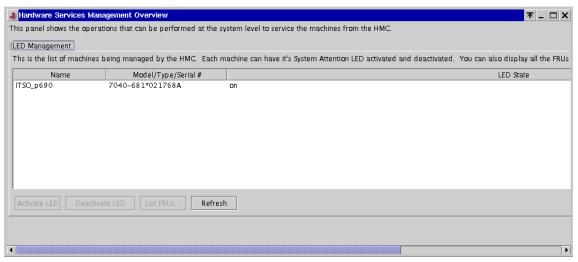

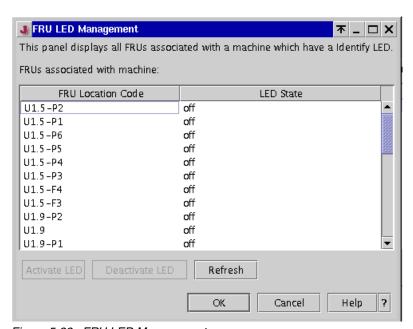

| 5-31 | Hardware Service Functions overview                            | 200 |

| 5-32 | FRU LED Management                                             | 200 |

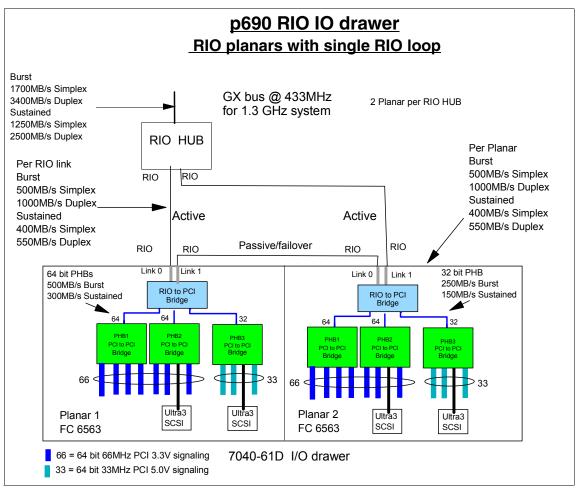

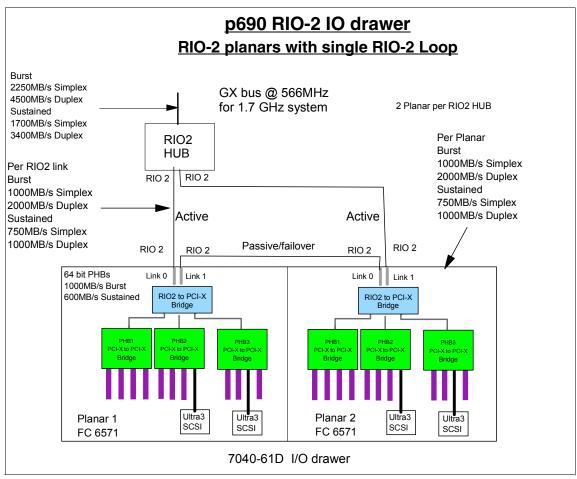

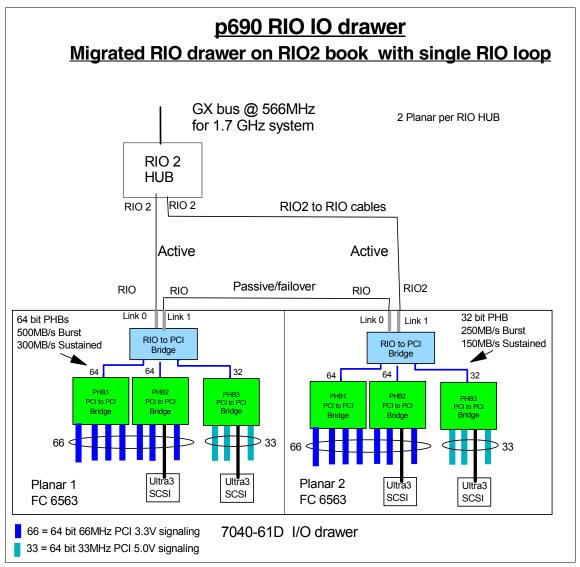

| B-1  | RIO drawer, in single-loop mode on a 1.3 GHz server            | 218 |

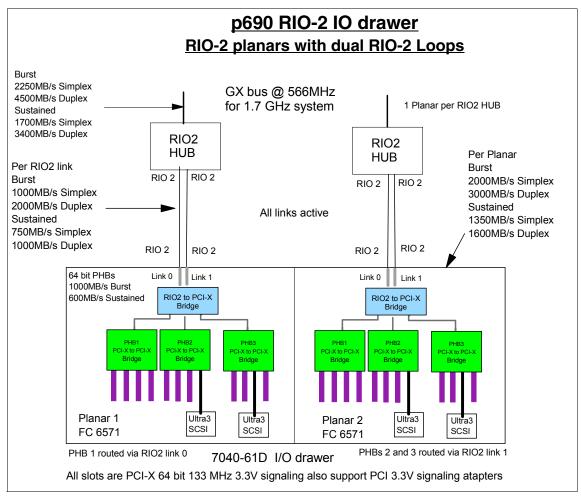

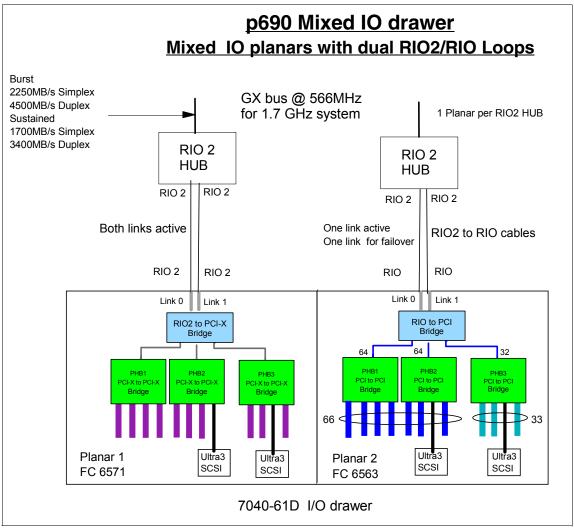

| B-2  | RIO-2 drawer, in dual-loop mode on a 1.7GHz server             | 219 |

| B-3  | RIO-2 drawer, in single-loop mode on a 1.7 GHz server          | 220 |

| B-4  | Mixed RIO/RIO-2 drawer, in dual-loop mode on a 1.7 GHz server  | 221 |

| B-5  | Migrated single-loop mode on a 1.7 GHz server                  | 222 |

| B-6  | Configuration for maximum bandwidth                            | 223 |

| B-7  | Configuration for maximum number of adapters and disks         | 224 |

| B-8  | Configuration after migration to RIO-2 Books without recabling | 225 |

X

# **Tables**

| 1-1  | Differences between pSeries 670 and pSeries 690             | 10  |

|------|-------------------------------------------------------------|-----|

| 1-2  | Comparison of AIX and Linux support for RAS features        | 14  |

| 2-1  | pSeries 690 main subsystems                                 | 18  |

| 2-2  | Supported combinations of processors                        | 23  |

| 2-3  | Relationship between MCMs, L3 cache, memory slots, and size | 35  |

| 2-4  | Supported memory cards configurations                       | 36  |

| 2-5  | Relationship between MCMs, RIO ports, and I/O drawers       | 42  |

| 2-6  | Supported memory configurations for pSeries 670             | 44  |

| 2-7  | Relationship between MCMs, RIO ports, and I/O drawers       | 45  |

| 2-8  | Maximum configuration for each cabling pattern              | 60  |

| 2-9  | Physical I/O book ports and system logical port numbers     | 62  |

| 2-10 | Available I/O ports versus installed MCM and Books          | 63  |

| 2-11 | Physical location code of drawer position number            | 70  |

| 3-1  | Physical memory size and number of allocatable partitions   | 87  |

| 4-1  | CUoD processor feature codes                                | 138 |

| 4-2  | Supported 1.1 and 1.3 GHz CUoD processor combinations       | 139 |

| 4-3  | Supported 1.5 and 1.7 GHz CUoD processor combinations       | 140 |

| 4-4  | CUoD memory feature codes                                   | 141 |

| 4-5  | CUoD error codes and messages                               | 146 |

| 5-1  | Hot-swappable FRUs                                          | 173 |

| 5-2  | Authentication process                                      | 202 |

# **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy, modify, and distribute these sample programs in any form without payment to IBM for the purposes of developing, using, marketing, or distributing application programs conforming to IBM's application programming interfaces.

#### **Trademarks**

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

**AIX®** ibm.com® AIX 5L™ IBMLink™ AS/400® iSeries™ Chipkill™ POWER2™ **ESCON®** POWER4™ eServer™ POWER4+™ **⊘**server™ POWERparallel® **@**server ™ PowerPC® **IBM®** pSeries™

Redbooks(logo)™ Redbooks™

RS/6000®

S/370™

S/390®

SP™

zSeries®

The following terms are trademarks of other companies:

ActionMedia, LANDesk, MMX, Pentium and ProShare are trademarks of Intel Corporation in the United States, other countries, or both.

Microsoft, Windows, Windows NT, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Java and all Java-based trademarks and logos are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

C-bus is a trademark of Corollary, Inc. in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries.

SET, SET Secure Electronic Transaction, and the SET Logo are trademarks owned by SET Secure Electronic Transaction LLC.

Other company, product, and service names may be trademarks or service marks of others.

# **Preface**

This IBM® Redbook explains the IBM @server™ pSeries™ 670 Model 671 and the IBM @server pSeries 690, a new level of UNIX servers providing world-class performance, availability, and flexibility. Capable of data center, application, and high performance computing, these servers include mainframe-inspired self-management and security to meet your most demanding needs.

This redbook includes the following topics:

- Overview of the pSeries 670 and pSeries 690

- ► Hardware architecture of the pSeries 670 and pSeries 690

- Using the IBM Configurator for e-business

- Capacity Upgrade on Demand

- Reliability, availability, and serviceability

This book is an ideal desk-side reference for IBM professionals, Business Partners, and technical specialists who support the pSeries 670 and pSeries 690, and for those who want to learn more about this radically new server in a clear, single-source handbook. It provides the necessary information to successfully order a pSeries 670 or pSeries 690 for a production environment and then, upon successful installation, configure service support functions, such as Service Focal Point and Inventory Scout.

#### The team that wrote this redbook

This IBM Redbook was produced by a team of specialists from around the world working at the International Technical Support Organization, Austin Center.

**Keigo Matsubara** is an Advisory IT Specialist at the International Technical Support Organization (ITSO), Austin Center. Before joining the ITSO, he worked in the System and Web Solution Center in Japan as a Field Technical Support Specialist (FTSS) for pSeries. He has been working for IBM for ten years.

Alvin Hua Juay Teng is a Technical Sales Specialist at IBM Singapore. He joined IBM in 2000 and has been working with pSeries ever since. He has experience in providing solutions for the banking industries and government organizations. He holds a master's degree in High Performance Computing for Engineered Systems from Singapore-MIT Alliance (A jointed master's degree from Singapore University of Singapore, Singapore, Nanyang Technological

University, Singapore, and Massachusetts Institute of Technology, US) and a B.Eng in Mechanical Engineering from University of Sheffield, UK.

Bruno Blanchard is a Certified IT Specialist working for IBM France at the IGS Pan-EMEA Infrastructure and Technology Group, in La Gaude. He holds an Engineering degree from Ecole Centrale de Paris and a master's degree from Oregon State University. He has been with IBM since 1983, as a System Engineer for VM and AIX®. He is a certified AIX and SP™ Specialist, and his areas of expertise also include pSeries servers and clusters, as well as network management. He is currently working as an Architect on projects deployed in Europe for the IBM @server cluster 1600 and pSeries servers required for the IBM IT infrastructure.

Thanks to the following people for their contributions to this project:

International Technical Support Organization, Austin Center Scott Veter and Wade Wallace

International Technical Support Organization, Rochester Center Gabrielle Velez

#### **IBM Austin**

Alan Standridge, Andy McLaughlin, Bill Casey, Bob Foster, Bruce Wood, Dave Willoughby, Doug Bossen, Eric Marshall, Iggy Haider, James Donnelly, Joel M. Tendler, John Bissell, John Purcell, Kaena Freitas, Mark Dewalt, Mike Stys, Minh Nguyen, Richard Bolton, Truc Nguyen, Walter Lipp

#### IBM Endicott

Scott Nettleship and Lenny Nichols

#### IBM Poughkeepsie

James T Mitchell

#### IBM Rochester

David L Shaw, Lawny Miller, Matt Spinler, Sandy Shirk-Heath

## Become a published author

Join us for a two- to six-week residency program! Help write an IBM Redbook dealing with specific products or solutions, while getting hands-on experience with leading-edge technologies. You will team with IBM technical professionals, Business Partners and/or customers.

Your efforts will help increase product acceptance and customer satisfaction. As a bonus, you'll develop a network of contacts in IBM development labs, and increase your productivity and marketability.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

#### **Comments welcome**

Your comments are important to us!

We want our Redbooks<sup>™</sup> to be as helpful as possible. Send us your comments about this or other Redbooks in one of the following ways:

▶ Use the online **Contact us** review redbook form found at:

ibm.com/redbooks

Send your comments in an Internet note to:

redbook@us.ibm.com

Mail your comments to:

IBM Corporation, International Technical Support Organization Dept. JN9B Building 003 Internal Zip 2834 11400 Burnet Road Austin, Texas 78758-3493

# **Summary of changes**

This section describes the technical changes made in this edition of the book and in previous editions. This edition may also include minor corrections and editorial changes that are not identified.

Summary of Changes for SG24-7040-02 for IBM @server pSeries 670 and pSeries 690 System Handbook as created or updated on March 29, 2005.

# **April 2003, Third Edition**

This revision reflects the addition, deletion, or modification of new and changed information described below.

#### **New information**

- ► AIX 5L Version 5.2

- Linux information on the pSeries 670 and pSeries 690

- ► POWER4<sup>TM</sup>+ processors

- New I/O subsystem

- Capacity Upgrade on Demand for memory

- ► How to update HMC

- ► Microcode update service

#### **Changed information**

- Using the IBM Configurator for e-business

- Capacity Upgrade on Demand for processors

- Description of On/Off Capacity on Demand

## October 2002, Second Edition

The second version of this book, SG24-7040-01 IBM @server pSeries 670 and pSeries 690System Handbook, was written by the following authors:

Keigo Matsubara, Bas Hazelzet, Marc-Eric Kahle

This revision reflects the addition, deletion, or modification of new and changed information described below.

#### **New information**

- ► The IBM @server pSeries 670 Model 671

- Capacity Upgrade on Demand

- Overview of the feature codes

#### **Changed information**

- ▶ Detailed logical partitioning explanation was moved to *The Complete Partitioning Guide for IBM* @server pSeries Servers, SG24-7039.

- ► Usage examples about how to use IBM Configurator for e-business were updated to include the IBM @server pSeries 670 Model 671.

- ► A new explanation was added about service functions, such as Service Focal Point and Inventory Scout.

- ► The CUoD support for AIX 5L Version 5.1 was added.

The following list shows contributors for the first version of this book, SG24-7040-00 IBM @server pSeries 690 System Handbook:

#### **IBM Austin**

Alan Standridge, Andy McLaughlin, Bob Foster, Bruce Wood, Dave Lewis, Dave Willoughby, Doug Bossen, George W Clark, James Donnelly, Jane Chilton, John O'Quin, John Purcell, Larry Amy, Luke Browning, Mark Dewalt, Mike Stys, Minh Nguyen, Sajan Lukose, Siraj Ismail, Susan Caunt, Truc Nguyen, Walter Lipp

#### **IBM Endicott**

Scott Nettleship and Lenny Nichols

#### **IBM Germany**

Knut Muennich

#### **IBM Hamden**

Jack Dobkowski

#### **IBM Poughkeepsie**

Anthony Pioli, Juan Parrilla II, Michael Schmidt, Rob Overton

#### **IBM Rochester**

Matt Spinler

#### **IBM UK**

Dave Williams and Clive Benjamin

## March 2002, First Edition

The first version of this book, SG24-7040-00 IBM @server pSeries 690 System Handbook, was written by the following authors:

Keigo Matsubara, Cesar Diniz Maciel, KangJin Lee, Martin Springer

The following list shows contributors for the first version of this book, SG24-7040-00 IBM @server pSeries 690 System Handbook:

#### **IBM Austin**

Alan Standridge, Andy McLaughlin, Arthur Ban, Balaram Sinharoy, Bob Foster, Bradley McCredie, Dave Willoughby, David Ruth, Doug Bossen, Duke Paulsen, Eric Marshall, Gerald McBrearty, Hung Le, Hye-Young McCreary, Jan Klockow, Joel M. Tendler, Julie Craft, Kurt Szabo, Luc Smolders, Mike Stys, Pat Buckland, Randy Itskin, Richard Cutler, Robert W West, Steve Dodson, Steve Fields, Steven Hartman, Susan Caunt, Walter Lipp, William Hodges

#### **IBM Japan**

Shigeru Kishikawa and Shingo Matsuda

#### IBM Poughkeepsie

Ron Goering

# 1

# Overview of the pSeries 670 and pSeries 690

The IBM @server pSeries 670 Model 671 (hereafter referred to as pSeries 670) and the IBM @server pSeries 690 (hereafter referred to as pSeries 690) are integral parts of the IBM @server product line, featuring servers that can help lower total cost of ownership, improve efficiency, and speed up e-business transformation.

The pSeries 670 and pSeries 690 are IBM's flagship products in the pSeries line of UNIX servers. The pSeries 670, a 4-way to 16-way server, and the pSeries 690, an 8-way to 32-way server, share the same basic technology, and represent the latest generation of performance leadership and reliability from IBM. They incorporate the latest advances in chip technology from IBM, as well as many leading self-managing system capabilities to enable mission-critical operation.

In addition to unparalleled speed, the pSeries 670 and pSeries 690 systems have the ability to consolidate critical applications on a single, data center class server. As a result, there are fewer servers to manage and maintain. Available capacity can be used more effectively and with greater flexibility by the dynamic logical partitioning function to meet changing business demands.

In this chapter we introduce the pSeries 670 and pSeries 690 servers, highlighting their advantages, main characteristics and components, as well as how they fit into the data center.

# 1.1 What's new in the pSeries 670 and pSeries 690

This third edition of the *IBM* @server *pSeries* 670 and *pSeries* 690 System Handbook, SG24-7040 describes these two models of servers, as available after the products' announcements in May 2003, that brings the following new features<sup>1</sup>:

- ▶ Processors using the POWER4+ chip, at 1.5 and 1.7 GHz

- ▶ L3 Cache and memory modules running at 500 and 575 MHz

- 64 GBs memory modules

- A faster I/O subsystem, using new I/O books, new RIO cables, new I/O drawer planar

- ► Support for 133 MHz PCI-X

- Improved partitioning facility, with support up to 32 partitions

- Improved Capacity Upgrade on Demand addressing both the processor and the memory resources

- new upgrades possibilities, including model conversion from pSeries 670 to pSeries 690

- Firmware updates from the HMC

The support of these new features leaves the general architecture of the pSeries 670 and pSeries 690 servers unchanged. However, it results into many important implementation changes, such as the RIO drawer cabling, the PCI adapters supported combinations, or the manner to use the IBM Configurator for e-business to order a new server or an MES (Miscellaneous Equipment Specification).

If you are already familiar with the pSeries 670 and pSeries 690 servers, you can avoid reading their general presentation in the following sections, and directly skip to the following chapters.

If however you are new to the pSeries 670 and pSeries 690 servers, we strongly encourage you to read this introductory chapter in its entirety.

**Note:** Throughout this book, we use the word "POWER4" to refer to the 1.1, 1.3, 1.5 or 1.7 GHz processors when the technology or speed difference is not of importance, and we specify "POWER4+" to refer exclusively to the 1.5 and 1.7 GHz processors.

<sup>&</sup>lt;sup>1</sup> Please check the announcement letter for the exact availability date of each new feature.

# 1.2 pSeries 670 and pSeries 690 characteristics

The pSeries 670 and pSeries 690 family of servers incorporate advanced technologies available from across the IBM @server family, as well as technology enhancements from IBM research divisions. The result are high-performance, high-availability servers that offer enhanced features and benefits.

The pSeries 670 and pSeries 690 servers are based on a modular design. They feature a Central Electronics Complex (CEC) (where memory and processors are installed), power subsystem, and I/O drawers, also known as Remote I/O (RIO) drawers. Optional battery backups can provide energy for an emergency shutdown in case of a power failure.

The CEC provides room for up to 16 POWER4 chips, each one housing two processors and a shared level 2 (L2) cache. The POWER4 chip offers an advanced microprocessor design, with an SMP design in a single silicon substrate.

Advanced multichip module (MCM) packaging places four POWER4 chips with four or eight processors, mounted on a ceramic package. This provides enhanced processor reliability, and faster interconnections between processors and L2 caches. Each MCM connects to two memory card slots through the level 3 (L3) cache modules.

Redundant power supplies and optional battery backups assure that a single power failure does not interrupt system operation. In case of total power failure, an emergency shutdown is initiated whenever the battery is present. The redundant power supplies are connected through separate power cords, in order to prevent a single failure on the external electrical circuit.

Building on IBM @server zSeries® heritage, the pSeries 670 and pSeries 690 deliver true logical partitioning and can be divided respectively into up to 16 or 32 partitions², each with its own set of system resources, such as processors, memory, and I/O. Unlike partitioning techniques available on other UNIX servers, logical partitioning provides greater flexibility and finer granularity. Resources can be assigned in any amount or combination for business-critical applications. Each logical partition has its own version of an operating system, being either AIX 5L Version 5.1, AIX 5L Version 5.2, or Linux.

The following sections detail some of the technologies behind the pSeries 670 and pSeries 690.

<sup>&</sup>lt;sup>2</sup> The number of LPAR that can be instantiated on a system depends on its hardware configuration. Please refer to the *The Complete Partitioning Guide for IBM* @server pSeries Servers, SG24-7039 for explanation of the LPAR configuration rules, and to 2.3.6, "I/O books" on page 47 in this redbook.

#### 1.2.1 Microprocessor technology

The POWER4 chip is a result of advanced research technologies developed by IBM. Numerous technologies are incorporated into the POWER4 to create a high-performance, high-scalability chip design to power future IBM @server pSeries systems. Some of the advanced techniques used in the design and manufacturing processes of the POWER4 include copper interconnects and Silicon-on-Insulator.

#### Copper interconnects

As chips become smaller and faster, aluminum interconnects, which have been used in chip manufacturing for over 30 years, present increasing difficulties. In 1997, after nearly 15 years of research, IBM scientists announced a new advance in the semiconductor process that involves replacing aluminum with copper. Copper has less resistance than aluminum, which permits the use of smaller circuits with reduced latency that allows for faster propagation of electrical signals. The reduced resistance and heat output make it possible to shrink the electronic devices even further while increasing clock speed and performance without resorting to exotic chip cooling methods.

#### Silicon-on-Insulator

Silicon-on-Insulator (SOI) refers to the process of implanting oxygen into a silicon wafer to create an insulating layer and using an annealing process until a thin layer of SOI film is formed. The transistors are then built on top of this thin layer of SOI. The SOI layer reduces the capacitance effects that consume energy, generate heat, and hinder performance. SOI improves chip performance by 25 to 35 percent.

Detailed information on the POWER4 chip can be found in 2.3.1, "POWER4 processor and MCM packaging" on page 22.

#### 1.2.2 Memory subsystem

The memory hierarchy in pSeries 670 and pSeries 690 systems is represented as follows:

Internal level 1 (L1) caches Each microprocessor core has its own L1

instruction and L1 data caches.

**Shared L2 cache** Inside a POWER4 chip, both processor cores

share an L2 cache.

#### L3 cache

It operates at a 3:1 ratio with the clock speed, and connects to the MCMs through a dedicated port. Each L3 cache module has a direct connection with one POWER4 chip and one memory slot.

The memory used in the pSeries 670 and pSeries 690 systems is Double Data Rate (DDR), which provides superior bandwidth. The minimum memory in the pSeries 670 system is 4 GB, in the pSeries 690 it is 8 GB, and it can be expanded to up to 256 GB and 512 GB, respectively. The pSeries 670 and pSeries 690 are the first pSeries servers to incorporate level 3 (L3) cache. This contributes to faster data access and faster processing capabilities.

Additional information about memory can be found in 2.3.2, "Memory subsystem for pSeries 690" on page 29, and in 5.4.2, "Memory redundancy mechanisms" on page 164.

#### 1.2.3 I/O drawer subsystem

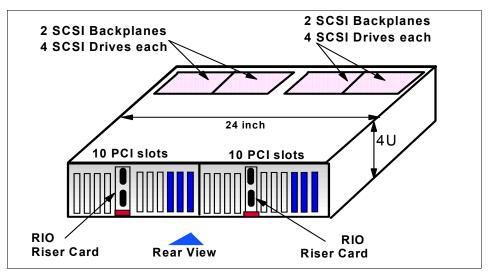

The standard system comes with one I/O drawer that features 20 Hot-Plug PCI slots, and supports more than 2.3 TB of storage located in 16 drive bays connected to integrated Ultra3 SCSI controllers. All power, thermal control, and communication systems have redundancy to eliminate outages caused by single component failures. Each I/O drawer connects to the system through two or four RIO ports, with up to 8 GB/s of total burst bandwidth per drawer<sup>3</sup>.

Up to three drawers can be added to the pSeries 670 to obtain a total of 60 PCI slots and more than 7 TB of internal disk storage. The pSeries 690 can accommodate up to eight drawers, supporting a total of 160 PCI slots and more than 18 TB of internal disk storage. For more information on the I/O subsystem, please refer to 2.4, "I/O subsystem" on page 51.

<sup>&</sup>lt;sup>3</sup> In the case of an RIO drawer connected to the CEC through two RIO loops.

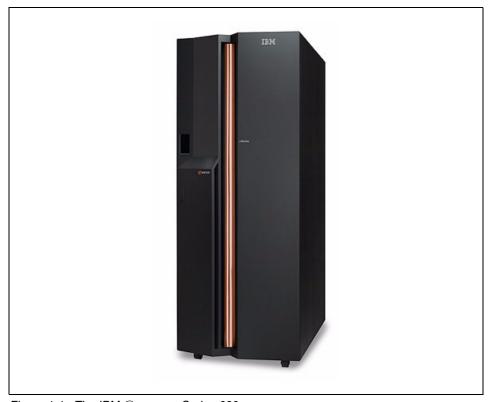

A picture of the IBM @server pSeries 690 is shown in Figure 1-1.

Figure 1-1 The IBM @server pSeries 690

#### 1.2.4 Hardware technology

The pSeries 690 introduces several advanced technologies into its design, and implements other available technologies with enhancements, truly delivering mainframe-class reliability and an outstanding performance. Some key technologies used are referenced here, as follows:

- ▶ Many self-healing, self-optimizing, and fault-avoidance mechanisms.

- ► zSeries packaging and power distribution, recognized as highly reliable.

- ► Advanced microprocessor design, with POWER4 dual processors, and multichip module (MCM) packaging.

- Logical partitioning (LPAR) offers true flexibility when selecting resources for partitions, and dynamic logical partitioning (DLPAR) allows for moving resources non-disruptively between logical partitions.

The pSeries 670 and pSeries 690 systems are the most reliable UNIX servers ever built, with the pSeries 690 the most powerful UNIX machine on the market. To achieve the outstanding capabilities that these servers offer, IBM has combined two methods to select the technology: Developing new technology, and enhancements to existing technology.

Developing new technologies is one of the most challenging tasks, especially in the high-end UNIX market. It means increased risks, because of the cost of development and the possibility of missing the product release schedule. As a huge technological step in the high-end UNIX market, IBM developed several new technologies for the pSeries 690, such as the POWER4 processor and distributed switch technology. These technologies are now used across the whole range of the pSeries Family, from the entry model pSeries 610 to the high-end pSeries 690 and the clustered model pSeries 655. Hardware technology is shared with the IBM *⊗* server iSeries<sup>™</sup>.

Enhancing existing technologies is an excellent way to exploit solutions already developed, and add new functions and features. It enables technology reuse, lowering costs and enabling a new product to use the best technology available for each specific requirement. The zSeries power subsystem and packaging and the MCM design are among those technologies that have been enhanced on the pSeries 670 and pSeries 690.

# 1.3 Logical partitioning

There is a strong demand for high-end systems to provide greater flexibility, in particular the ability to subdivide them into smaller partitions that are capable of running a version of an operating system or a specific set of application workloads.

IBM initially started work on partitioning S/370™ mainframe systems in the 1970s. Since then, logical partitioning on IBM mainframes (now called IBM @server zSeries) has evolved from a predominantly physical partitioning scheme based on hardware boundaries, to one that allows for virtual and shared resources with dynamic load balancing. In 1999 IBM implemented LPAR support on the AS/400® (now called IBM @server iSeries) platform. In 2000 IBM announced the ability to run the Linux operating system in an LPAR or on top of VM on a zSeries server, to create thousands of Linux instances on a single box.

Throughout this publication we refer to the different partitioning mechanisms available on the market. Therefore, it is appropriate to clarify the terms and definitions by which we classify these mechanisms.

- ▶ A *building block* is a collection of system resources, such as CPUs, memory, and I/O connections. These may be physically packaged as a self-contained SMP system (rack-mounted or stand-alone) or as boards within a larger multiprocessor system. There is no requirement for the CPUs, memory, and I/O slots to occupy the same physical board within the system, although they often do. Other vendors use the terms *system board*, *cell*, and *Quad Building Block (QBB)* to refer to their building blocks.

- ▶ A *physical partition* consists of one or more building blocks linked together by a high-speed interconnect. Generally, the interconnect is used to form a single coherent memory address space. In a system that is only capable of physical partitioning, a partition is a group of one or more building blocks configured to support an operating system image. Other vendors may refer to physical partitions as *domains* or *nPartitions*.

- ► A *logical partition* is a subset of logical resources that are capable of supporting an operating system. A logical partition consists of CPUs, memory, and I/O slots that are a subset of the pool of available resources within a system.

**Note:** The major difference between logical partitioning and physical partitioning is the granularity and flexibility available for allocating resources to an operating system image. Logical partitions have finer granularities than physical partitions.

It should be noted that the zSeries LPAR implementation is unique in comparison to the other partitioning implementations available from IBM and other hardware vendors. It is the most mature and dynamic partitioning technology in the industry. IBM experience with physical and logical partitioning over the last 25 years has greatly influenced the design and implementation of logical partitioning on pSeries.

The pSeries 690 were the first pSeries servers to incorporate the ability to be partitioned (This is now also available on pSeries 630, 650, 655, and 670). Their architectural design brings true logical partitioning to the UNIX world, being capable of up to 32 partitions inside a single server, with great flexibility in resource selection. The partitioning implementation on the pSeries 670 and pSeries 690 differs from those of other UNIX system vendors in that the physical resources that can be assigned to a partition are not limited by internal physical system board boundaries.

Processors, memory, and I/O slots can be allocated to any partition, regardless of their locality. For example, two processors on the same POWER4 silicon chip can be in different partitions. PCI slots are assigned individually to partitions, and memory can be allocated in fixed-size increments. The granularity of the resources that can be assigned to partitions is very fine, providing flexibility to create systems with just the desired amount of resources.

The pSeries 670 and pSeries 690 systems can also be shipped with additional capacity, which may be purchased and activated at a certain point in time without affecting normal machine operation. This feature is referred to as Capacity Upgrade on Demand (CUoD), which provides flexibility and fine granularity in processor and memory upgrades. A feature that comes with CUoD is Dynamic Processor Sparing. This is the capability of the system to configure out a failing processor and configure in a non-activated CUoD processor. In this way, the number of activated processors is guaranteed by IBM whenever a processor failure would occur. Details on this new offering can be found in Chapter 4, "Capacity Upgrade on Demand" on page 133.

The pSeries 670 and pSeries 690 are also capable of running Linux inside a partition, and having both AIX 5L Version 5.1, AIX 5L Version 5.2, and Linux running on the system simultaneously. The pSeries 690 is the first high-end UNIX server capable of running Linux, and the only one supporting Linux concurrently with other operating systems.

For more information on logical partitioning technology on the pSeries 690, refer to the *Partitioning for the IBM* @server pSeries 690 *System* white paper, available at:

http://www.ibm.com/servers/eserver/pseries/hardware/whitepapers/lpar.html

Also refer to *The Complete Partitioning Guide for IBM* @server pSeries Servers, SG24-7039.

# 1.4 Dynamic logical partitioning

Starting from AIX 5L™ Version 5.2, IBM supports dynamic logical partitioning (also known as DLPAR) in partitions on several logical-partitioning capable IBM @server pSeries server models, including the pSeries 670 and pSeries 690. The dynamic logical partitioning function allows you to add and remove resources, such as CPUs, memory, and I/O slots, to and from a partition as well as to move resources between two partitions, without operating system reboot (on the fly). However, to use the function, the following conditions must be met, because it is achieved by the combination of these three components:

- ► The pSeries 670 and pSeries 690 systems must be updated with the 10/2002 system microcode update or later.

- ► The IBM Hardware Management Console for pSeries (HMC) must be updated with Release 3 or higher, and must be connected through Ethernet to the each partition.

- ► A partition that requires the dynamic logical partitioning function must be installed with AIX 5L Version 5.2, or must be migrated to AIX 5L Version 5.2 from AIX 5L Version 5.1.

# 1.5 General overview of pSeries 670 and pSeries 690

The pSeries 670 has some differences from the pSeries 690. Basically it has the same technical advantages and Reliability, Availability, and Serviceability (RAS) features, but it is a single rack server and has several configuration limitations compared to the pSeries 690. Table 1-1 provides a quick overview of the differences between these two models.

Table 1-1 Differences between pSeries 670 and pSeries 690

| Component                    | pSeries 690 | pSeries 670          |

|------------------------------|-------------|----------------------|

| Number of CPUs / MCMs        | 8-32/1-4    | 4-16/1-2             |

| 4 way 1.1GHz POWER4          | No          | Yes                  |

| 8 way 1.1GHz POWER4          | Yes         | Yes                  |

| 8 way 1.3GHz POWER4<br>Turbo | Yes         | No                   |

| 4 way 1.3GHz POWER4<br>HPC   | Yes         | No                   |

| 4 way 1.5GHz POWER4+         | No          | Yes                  |

| 8 way 1.5GHz POWER4+         | Yes         | Yes                  |

| 8 way 1.7GHz POWER4+         | Yes         | No                   |

| Amount of memory (GB)        | 8-512       | 4-256                |

| Number of memory cards       | 1-8         | 1-4                  |

| Number of I/O drawers        | 1-8         | 1/2 <sup>a</sup> - 3 |

| Number of PCI slots          | 20-160      | 10-60                |

| IBF feature                  | Yes         | Yes                  |

| Component       | pSeries 690 | pSeries 670 |

|-----------------|-------------|-------------|

| Number of racks | 1-2         | 1           |

a. As an initial order, just one half I/O drawer can be used with 10 PCI slots.

The MCMs used in the pSeries 670 are either 4- or 8-way modules. Since it is only possible to install two MCMs in the pSeries 670, only the inward-facing memory card slots can be used.

**Note:** It is possible to upgrade a pSeries 670 into a pSeries 690 by model conversion.

# 1.6 Market positioning

The pSeries 690 is one of the most powerful UNIX servers ever built, with the best performance per processor in many application areas. The same holds for the pSeries 670 in the midrange. From copper-based, Silicon-on-Insulator (SOI) POWER4 microprocessor technology and multichip packaging expertise to the industry's most advanced self-management capabilities, the pSeries 670 and pSeries 690 are designed to provide the ultimate in performance, configuration flexibility, and availability.

The pSeries 670 and pSeries 690 are positioned to fulfill the applications' need for performance and scalability, and the reliability required in mission-critical environments. It is an ideal server on which to run corporate applications such as Online Transaction Processing (OLTP), Enterprise Resource Planning (ERP), Business Intelligence (BI), and high-performance e-business infrastructures. It also provides attractive facilities for server consolidation with its flexible partitioning mechanism, as well as the dynamic logical partitioning function, possibilities, and advanced management functions.

Performance wise, the pSeries 670 and pSeries 690 excel in commercial processing, and the pSeries 690 set many new records in High Performance Computing (HPC) applications. The balanced architecture, together with high performance processors, offer unparalleled price/performance, helping to reduce costs not only on the server itself, but also on power, cooling, and software licenses.

In the case of very resource-consuming applications, or for consolidation of a very high number of servers, it is possible to group several pSeries 670 and pSeries 690 into clusters, (optionally with other pSeries, RS/6000® and SP servers) known as IBM @serverCluster 1600.

Additional clustering information can be found at:

http://www.ibm.com/servers/eservers/clusters/hardware/1600.html

For more information on the AIX 5L operating system and related IBM products, the following link may be of interest:

http://www.ibm.com/servers/aix/

For application availability on the AIX 5L operating system, the following link can be used for alphabetical listing and advanced search options, both for IBM software products and third-party software products.

http://www.ibm.com/servers/aix/products/

# 1.7 Supported operating systems

The goal of this redbook is to present the hardware features of the pSeries 670 and pSeries 690 servers. It does not have a designated chapter providing information about the operating systems that are supported on this hardware. However, throughout the book, when a feature requires a specific level of software, we will mention the prerequisite.

The following sections provide general information and pointers to the relevant documentation about operating systems you can run on these servers:

- "AIX 5L Version 5.1" on page 12

- "AIX 5L Version 5.2" on page 13

- "Linux SuSE" on page 13

#### 1.7.1 AIX 5L Version 5.1

When using AIX on pSeries 670 or pSeries 690, AIX 5L Version 5.1 is the minimum level that must be installed. It is the first version of AIX supporting the POWER 4 processor technology. Any prior version of AIX, including AIX 4.3.3, is not supported on pSeries 670 or pSeries 690.

AIX 5.1 provides support for the features that were announced on the first generation of pSeries 690. It therefore does not support some of the features that were announced later. In particular, AIX 5.1 does not support:

- Dynamic LPAR

- Memory Capacity Upgrade on Demand

- Dynamic Processor Sparing

- Dynamic CPU Guard

While models that support greater than 256 GB memory sizes have the potential to define greater than 256 GB logical partition sizes, AIX 5.1 logical partitions have a maximum logical partition memory size of 256 GB. AIX 5.1 partitions defined to have greater than 256 GB would fail to activate with an insufficient real mode memory failure. AIX 5.2 and Linux partitions can be greater than 256 GB in size.

#### 1.7.2 AIX 5L Version 5.2

AIX 5L Version 5.2 is the latest available version of AIX. As a general rule, all features available with the pSeries 670 or pSeries 690 are supported by this level of AIX. Some features may require a specific maintenance level.

#### 1.7.3 **Linux - SuSE**

The Linux distribution which is supported on the pSeries 670 or pSeries 690 is the SuSE Linux Enterprise Server 8. Other distributions of Linux are not officially supported on pSeries 670 or pSeries 690, although some distributors have announced their intention to port their products to this hardware platform.

To find the latest information about the Linux products supported on pSeries, refer to these Web sites:

```

http://www.ibm.com/servers/eserver/pseries/linux/

http://www.ibm.com/servers/eserver/pseries/linux/whitepapers/linux_pseries.pdf

```

Information about SuSE Linux Enterprise Server 8 can be found at:

http://www.suse.com/us/business/products/server/sles/i pseries.html

Release notes for the SuSE Linux Enterprise Server 8 are available at:

http://www.ibm.com/servers/eserver/pseries/linux/sles8 release notes.pdf

There are some restrictions that you must be aware of regarding Linux on pSeries 670 or pSeries 690:

- ► Linux-SuSE can only be installed on partitions and not supported on the Full System Partition.

- Only a subset of the hardware options (disks, adapters, ...) are supported. For the latest list of supported features, refer to:

```

http://www.ibm.com/servers/eserver/pseries/hardware/linux facts.pdf

```

- ► We do not recommend using Linux in partition with a large number of processors. Usually, Linux applications perform at their best with less than 4 to 8 processors in the partition.

- ► CuOD is not available for Linux systems.

Redbooks are available that specifically address the topic of Linux on pSeries. In particular, we recommend that you read *Linux Applications on pSeries*, SA24-6033, for information about installing Linux on pSeries 670 or pSeries 690, or porting Linux applications onto AIX using the AIX toolbox for Linux applications.

## 1.7.4 Comparison of RAS supported features

The hardware and firmware of pSeries 670 or pSeries 690 provides for many RAS features, which are described in Chapter 5, "Reliability, availability, and serviceability" on page 157.

Table 1-2 Comparison of AIX and Linux support for RAS features

| RAS functions             | AIX | Linux   |

|---------------------------|-----|---------|

| Service Focal Point       | Yes | No      |

| I/O Errors Reporting      | Yes | Yes     |

| EEH Detection             | Yes | Yes     |

| EEH Recovery              | Yes | No      |

| Concurrent Diagnostics    | Yes | No      |

| Hot Plug (I/O, SCSI)      | Yes | No      |

| Inventory Scout           | Yes | No      |

| Update System Firmware    | Yes | Yes     |

| Update IOA Firmware       | Yes | No      |

| Platform errors to syslog | Yes | Yes     |

| EPOW Warnings             | Yes | No      |

| Iscfg                     | Yes | Partial |

| Scan Dump                 | Yes | Yes     |

| DASD Mirroring            | Yes | No      |

| Service Agent             | Yes | No      |

| Error Log Analysis        | Yes | No      |

| Predictive callout        | Yes | No      |

| Dynamic CPU Deallocation  | Yes | No      |

| snap                      | Yes | Yes     |

| RAS functions                                 | AIX | Linux |

|-----------------------------------------------|-----|-------|

| Isvpd                                         | Yes | Yes   |

| Ismcode                                       | Yes | Yes   |

| SRC codes(IPL prog, Machine check, dump state | Yes | No    |

| HACMP Options                                 | Yes | No    |

The RAS features also need some support by the operating system, so that the system administrator can use them. Table 1-2 on page 14 lists which features are available in AIX or Linux.

Some features may require a specific maintenance level of code to be supported.

For many features that are not supported by Linux, there are statements of the direction for support in future versions of the operating system.

#### 1.7.5 Installation and backup of the operating systems

For a pSeries 670 or pSeries 690, all internal media bays on the front are connected to one I/O slot, while all internal media bays in the back are connected to another I/O slot. Therefore, a maximum of two partitions can be directly connected to a set of internal media bays at any one time. In many cases, because of the performance and flexibility of the systems, more than two partitions are configured on a pSeries 670 or pSeries 690. In this section, we briefly describe the three following options to install and back up multiple partitions on a pSeries 670 or pSeries 690.

- Share over time a set of internal media (CD-ROM and tape drive) between all the partitions. This option is likely to have the lowest cost and works with both AIX and Linux. But note that unless you are running AIX 5L Version 5.2, you would need to shutdown the partitions that are affected when transferring the media bays from one partition to another. Another point to take into account is that at any one time, a maximum of two partitions can be installed or backed up if you have the maximum number of internal media bays.

- ▶ Provide a set of media (CD-ROM and tape drive) for each partition. If there is more than two partitions, you need to configure additional external CD-ROM, tape drives and the required adapters on the I/O drawers. This option can be used for both AIX and Linux. The advantage if this option is that all the partitions can be scheduled to be backed up at the same time or different times, but there is an additional cost for the external devices.

- ► Provide a set of internal media to a partition and use the AIX Network Installation Manager (NIM) to install and manage the partitions. This option is only supported with AIX. NIM provides capabilities, such as installation, fixes

through the network, and also creates system backups using the **mksysb** command. For more details about NIM, refer to *The Complete Partitioning Guide for IBM @*server pSeries Servers, SG24-7039.

# Hardware architecture of the pSeries 670 and pSeries 690

Both the pSeries 670 and pSeries 690 are based on a modular design, where all components are mounted in one or two 24 inch racks. There are three major subsystems: the Central Electronics Complex (CEC), the power subsystem, and the I/O subsystem. In addition, all these components are managed by an external management workstation, called the Hardware Management Console (HMC). Each of these subsystems and the HMC are explained in detail in this chapter:

- ▶ 2.3, "Central Electronics Complex" on page 19

- ► 2.4, "I/O subsystem" on page 51

- ▶ 2.5, "Power subsystem" on page 72

- ▶ 2.6, "IBM Hardware Management Console for pSeries" on page 75

The pertinent information about the differences between the pSeries 690 and the pSeries 670 is also provided in this chapter.

The support of the Capacity Upgrade on Demand feature on the pSeries 670 and pSeries 690 servers requires some specific hardware features and introduces additional configuration rules. All CUoD specific aspects are described in Chapter 4, "Capacity Upgrade on Demand" on page 133, and are not addressed in this chapter.

## 2.1 What's new in the pSeries 670 and pSeries 690

In May 2003, IBM has announced new hardware features on the pSeries 690 and pSeries 670 servers:

- ▶ In addition to the 1.1GHz and 1.3 GHz chip using POWER4 technology, the customer can now also choose processors using the POWER4+ technology, with a clock speed of 1.5 or 1.7 GHz. These new processors are described in 2.3.1, "POWER4 processor and MCM packaging" on page 22, as well as their new associated L3 cache modules.

- ► As for the L3 cache, new memory modules are announced, that support a faster clock speed to be used with the new POWER4+ processors. In addition, a larger 64 GB memory board is now supported. These memory modules and the new configuration possibility they offer are described in 2.3.2, "Memory subsystem for pSeries 690" on page 29 and 2.3.4, "Memory subsystem for pSeries 670" on page 42.

- ▶ A completely new I/O subsystem, using a faster technology (called RIO-2), is mandatory to support the new POWER4+ processors, and can also be used in conjunction with the POWER4 processors. It consists of new I/O books, described in 2.3.6, "I/O books" on page 47, new I/O planers for the RIO drawers (see 2.4.1, "I/O drawer" on page 51), and a completely new set of cabling options between the I/O books and the RIO drawers, explained in 2.4.2, "I/O subsystem communication and monitoring" on page 56.

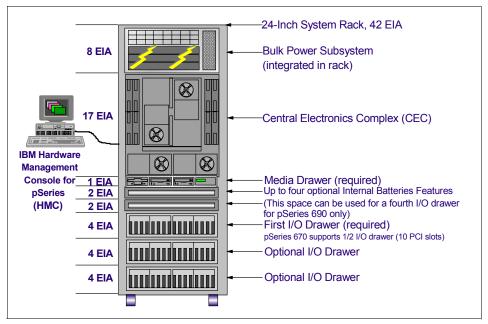

# 2.2 Modular design of the pSeries 670 and pSeries 690

Both the pSeries 670 and pSeries 690 are rack-based servers, housed on the same 24-inch wide, 42 EIA height rack used by the IBM @server zSeries. Inside this rack all the server components are placed in specific positions. This design and mechanical organization offers advantages in optimization of floor space usage.

Table 2-1 shows the main subsystems of the pSeries 690 and pSeries 670, and the sections where they are described.

| Table 2-1 pSeries 690 main subs |

|---------------------------------|

|---------------------------------|

| Subsystem name                    | Section number                                                      |

|-----------------------------------|---------------------------------------------------------------------|

| Central Electronics Complex (CEC) | 2.3, "Central Electronics Complex" on page 19                       |

| I/O subsystem                     | 2.4, "I/O subsystem" on page 51<br>2.4.4, "Media drawer" on page 70 |

| Power subsystem                   | 2.5, "Power subsystem" on page 72                                   |

A representation of these components inside the base rack is shown in Figure 2-1.

Figure 2-1 The pSeries 670 and pSeries 690 base rack with components

# 2.3 Central Electronics Complex

The Central Electronics Complex is a 17 EIA height drawer housing the processors and memory of the pSeries 670 and pSeries 690. The CEC contains the following components:

- ► The CEC backplane, where the components are mounted

- ► The multichip modules (MCMs), which contain the POWER4 processors

- Memory cards

- ▶ L3 cache modules

- ► I/O books, which provide the Remote I/O (RIO) ports for the I/O drawers, and the service processor function

- Fans and blowers for CEC cooling

Major design efforts have contributed to the development of the pSeries 670 and pSeries 690 to analyze single points of failure within the CEC to either eliminate them or to provide hardening capabilities to significantly reduce their probability of failure.

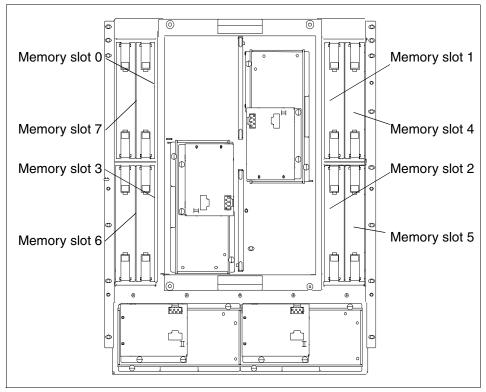

The front view of CEC is shown in Figure 2-2 on page 20. There are eight memory card slots available for pSeries 690 and four for pSeries 670. For detailed information about memory, see 2.3.2, "Memory subsystem for pSeries 690" on page 29, and 2.3.4, "Memory subsystem for pSeries 670" on page 42.

Figure 2-2 CEC front view