# $\mathsf{REACT}^{\scriptscriptstyle\mathsf{TM}}$ Real-Time Programmer's Guide

Document Number 007-2499-007

#### **CONTRIBUTORS**

Written by David Cortesi and Susan Thomas

Updated by Julie Boney

Illustrated by Gloria Ackley and Susan Thomas

Production by Chrystie Danzer

Engineering contributions by Rich Altmaier, Joe Caradonna, Jeffrey Heller, Ralph

Humphries, Bruce Johnson, Luis Stevens, and Don Hankins

© Copyright 1998, 2000 Silicon Graphics, Inc.— All Rights Reserved

The contents of this document may not be copied or duplicated in any form, in whole

or in part, without the prior written permission of Silicon Graphics, Inc.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and/or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor/manufacturer is Silicon Graphics, Inc., 2011 N. Shoreline Blvd., Mountain View, CA 94043-1389.

Silicon Graphics, the Silicon Graphics logo, CHALLENGE, Indy, IRIX, and Onyx are registered trademarks and IRIS Insight, Onyx 2, Origin 200, Origin 2000, Origin 3000, Performer, POWER CHALLENGE, POWER Channel, POWERpath, and REACT/Pro are trademarks of Silicon Graphics, Inc. R8000 and R10000 are registered trademarks of MIPS Technologies, Inc. AT&T and SVR4 are registered trademarks of AT&T. Tundra Universe is a trademark of Tundra Semiconductor Corporation. UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company, Ltd.

REACT™ Real-Time Programmer's Guide Document Number 007-2499-007

#### Contents

**List of Examples** xi

```

List of Figures xiii

List of Tables xv

About This Guide xvii

Who This Guide Is For xvii

What the Book Contains xviii

Other Useful Books and Sites xix

Reader Comments xx

1.

Real-Time Programs 1

Defining Real-Time Programs 1

Examples of Real-Time Applications 2

Simulators 2

Requirements on Simulators 3

Frame Rate 3

Transport Delay 3

Aircraft Simulators 3

Ground Vehicle Simulators 4

Plant Control Simulators 4

Virtual Reality Simulators 4

Hardware-in-the-Loop Simulators 5

Data Collection Systems 5

Requirements on Data Collection Systems 5

Real-Time Programming Languages 6

```

#### 2. How IRIX and REACT/Pro Support Real-Time Programs 7

```

Kernel Facilities for Real-Time Programs 8

Kernel Optimizations 8

Special Scheduling Disciplines 8

POSIX Real-Time Policies 8

Gang Scheduling 9

Locking Virtual Memory 9

Mapping Processes and CPUs 9

Controlling Interrupt Distribution 10

REACT/Pro Frame Scheduler 11

Synchronization and Communication 11

Shared Memory Segments 12

Semaphores 12

Locks 13

Mutual Exclusion Primitives 14

Signals 14

Signal Latency 15

Signal Families 15

Timers and Clocks 16

Hardware Cycle Counter 16

Interchassis Communication 17

Socket Programming 17

Message-Passing Interface (MPI) 17

Reflective Shared Memory 18

External Interrupts 18

```

#### 3. Controlling CPU Workload 19

Using Priorities and Scheduling Queues 19

Scheduling Concepts 20

Tick Interrupts 20

Time Slices 20

Understanding the Real-Time Priority Band 21

Understanding Affinity Scheduling 24

Using Gang Scheduling 25

Changing the Time Slice Duration 26

Minimizing Overhead Work 27

Assigning the Clock Processor 27

Unavoidable Timer Interrupts 28

Isolating a CPU From Sprayed Interrupts 28

Redirecting Interrupts 28

Understanding the Vertical Sync Interrupt 30

Restricting a CPU From Scheduled Work 30

Assigning Work to a Restricted CPU 33

Isolating a CPU From TLB Interrupts 34

Isolating a CPU When Performer Is Used 35

Making a CPU Nonpreemptive 35

Minimizing Interrupt Response Time 37

Maximum Response Time Guarantee 37

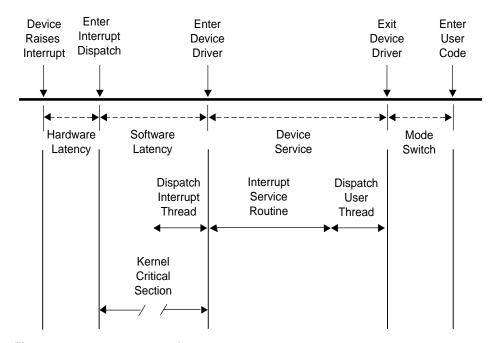

Components of Interrupt Response Time 37

Hardware Latency 38

Software Latency 39

Kernel Critical Sections 39

Device Service Time 40

Dispatch User Thread 40

Mode Switch 40

Minimal Interrupt Response Time 41

#### 4. Using the Frame Scheduler 43

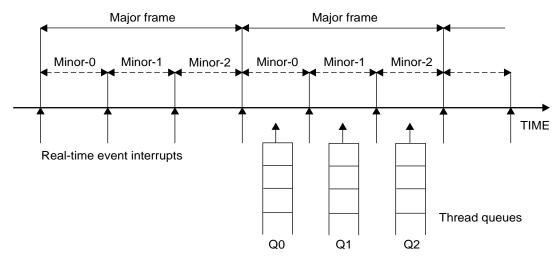

Frame Scheduler Concepts 44

Frame Scheduler Basics 44

Thread Programming Models 44

Frame Scheduling 45

The FRS Controller Thread 47

The Frame Scheduler API 48

Interrupt Information Templates 48

Library Interface for C Programs 50

System Call Interface for Fortran and Ada 52

Thread Execution 53

Scheduling Within a Minor Frame 54

Scheduler Flags frs\_run and frs\_yield 55

Detecting Overrun and Underrun 55

Estimating Available Time 56

Synchronizing Multiple Schedulers 56

Starting a Single Scheduler 57

Starting Multiple Schedulers 57

Pausing Frame Schedulers 58

Managing Activity Threads 58

Selecting a Time Base 59

On-Chip Timer Interrupt 60

High-Resolution Timer 60

Vertical Sync Interrupt 60

External Interrupts 61

Device Driver Interrupt 61

Software Interrupt 62

User-Level Interrupts 62

```

Using the Scheduling Disciplines 63

Real-Time Discipline 63

Background Discipline 64

Underrunable Discipline

Overrunnable Discipline 64

Continuable Discipline 65

Using Multiple Consecutive Minor Frames 65

Designing an Application for the Frame Scheduler 66

Preparing the System 67

Implementing a Single Frame Scheduler 68

Implementing Synchronized Schedulers

Synchronized Scheduler Concepts 69

Implementing a Master Controller Thread 70

Implementing Slave Controller Threads 71

Handling Frame Scheduler Exceptions 72

Exception Types 72

Exception Handling Policies 72

Injecting a Repeat Frame 73

Extending the Current Frame 73

Dealing With Multiple Exceptions 73

Setting Exception Policies 73

Querying Counts of Exceptions 75

Using Signals Under the Frame Scheduler 76

Signal Delivery and Latency 76

Handling Signals in the FRS Controller

Handling Signals in an Activity Thread 78

Setting Frame Scheduler Signals 78

Sequence Error 79

Using Timers with the Frame Scheduler 80

```

5.

6.

The PCI Bus 97

```

FRS Kernel-Level Device Driver Interface 80

Device Driver Overview 81

Registering the Initialization and Termination Functions 81

Frame Scheduler Initialization Function 82

Frame Scheduler Termination Function 84

Generating Interrupts 85

Optimizing Disk I/O for a Real-Time Program 87

Memory-Mapped I/O 87

Asynchronous I/O 88

Conventional Synchronous I/O 88

Asynchronous I/O Basics 88

Guaranteed-Rate I/O (GRIO) 89

Managing Device Interactions 91

Device Drivers 91

How Devices Are Defined 91

How Devices Are Used 92

Device Driver Entry Points 92

Taking Control of Devices 93

SCSI Devices 94

SCSI Adapter Support 94

System Disk Device Driver

System Tape Device Driver 95

Generic SCSI Device Driver 95

CD-ROM and DAT Audio Libraries 96

```

```

The VME Bus 98

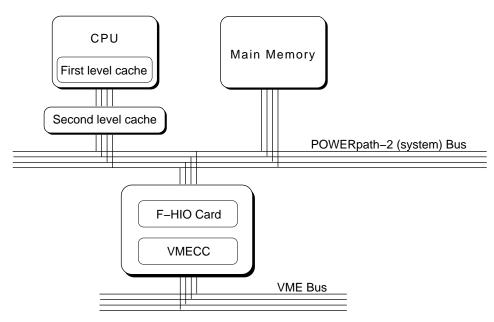

CHALLENGE an Onyx Hardware Nomenclature 98

VME Bus Attachments 99

VME Address Space Mapping 100

PIO Address Space Mapping 101

DMA Mapping 102

Program Access to the VME Bus 102

PIO Access 102

User-Level Interrupt Handling 103

DMA Access to Master Devices 103

DMA Engine Access to Slave Devices

Serial Ports 108

External Interrupts 109

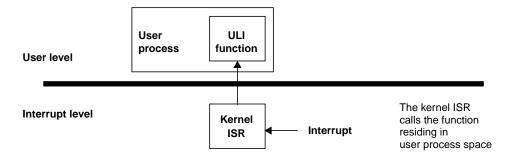

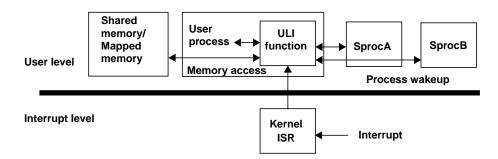

Managing User-Level Interrupts 111

Overview of ULI 112

The ULI Handler 112

Restrictions on the ULI Handler

Planning for Concurrency 114

Debugging With Interrupts

Declaring Global Variables 114

Using Multiple Devices 115

Setting Up 115

Opening the Device Special File 116

Locking the Program Address Space 116

Registering the Interrupt Handler 117

Registering an External Interrupt Handler 118

Registering a VME Interrupt Handler 118

Registering a PCI Interrupt Handler 119

Interacting With the Handler 119

Achieving Mutual Exclusion 120

Sample Programs 120

```

7.

#### A. Sample Programs 131

Basic Example 132

Real-Time Application Specification 132

Frame Scheduler Design 132

Example of Scheduling Separate Programs 133

Examples of Multiple Synchronized Schedulers 134

Example of Device Driver 136

Examples of a 60 Hz Frame Rate 136

Example of Managing Lightweight Processes 137

The simple\_pt Pthreads Program 137

Glossary 147

Index 155

### List of Examples

| Example 3-1  | Initiating Gang Scheduling 26                                   |

|--------------|-----------------------------------------------------------------|

| Example 3-2  | Setting the Time-Slice Length 26                                |

| Example 3-3  | Setting the Clock CPU 27                                        |

| Example 3-4  | Number of Processors Available and Total 32                     |

| Example 3-5  | Restricting a CPU 32                                            |

| Example 3-6  | Assigning the Calling Process to a CPU 33                       |

| Example 3-7  | Making a CPU nonpreemptive 36                                   |

| Example 4-1  | Skeleton of an Activity Thread 53                               |

| Example 4-2  | Alternate Skeleton of Activity Thread 54                        |

| Example 4-3  | Function to Set INJECTFRAME Exception Policy 74                 |

| Example 4-4  | Function to Set STRETCH Exception Policy 74                     |

| Example 4-5  | Function to Return a Sum of Exception Counts (pthread Model) 75 |

| Example 4-6  | Function to Set Frame Scheduler Signals 79                      |

| Example 4-7  | Minimal Activity Process as a Timer 80                          |

| Example 4-8  | Exporting Device Driver Entry Points 82                         |

| Example 4-9  | Device Driver Initialization Function 83                        |

| Example 4-10 | Device Driver Termination Function 84                           |

| Example 4-11 | Generating an Interrupt From a Device Driver 85                 |

| Example 6-1  | Memory Mapping With pciba 97                                    |

| Example 7-1  | Hypothetical PCI ULI Program 121                                |

| Example 7-2  | Hypothetical External Interrupt ULI Program 126                 |

### List of Figures

| Figure 3-1 | Real-Time Priority Band 22                       |

|------------|--------------------------------------------------|

| Figure 3-2 | Components of Interrupt Response Time 38         |

| Figure 4-1 | Major and Minor Frames 46                        |

| Figure 6-1 | Multiprocessor CHALLENGE Data Path Components 99 |

| Figure 7-1 | ULI Functional Overview 111                      |

| Figure 7-2 | ULI Handler Functions 114                        |

|            |                                                  |

### List of Tables

| Table 2-1 | Signal Handling Interfaces 15                                              |

|-----------|----------------------------------------------------------------------------|

| Table 3-1 | schedctl() Real-Time Priority Range Remapping 23                           |

| Table 4-1 | Frame Scheduler Operations 50                                              |

| Table 4-2 | Frame Scheduler schedctl() Support 52                                      |

| Table 4-3 | Signal Numbers Passed in frs_signal_info_t 78                              |

| Table 6-1 | Multiprocessor CHALLENGE VME Cages and Slots 99                            |

| Table 6-2 | POWER Channel-2 and VME bus Configurations 100                             |

| Table 6-3 | VME Bus PIO Bandwidth 103                                                  |

| Table 6-4 | VME Bus Bandwidth, VME Master Controlling DMA 104                          |

| Table 6-5 | VME Bus Bandwidth, DMA Engine, D32 Transfer (CHALLENGE/Onyx Systems) 106   |

| Table 6-6 | VME Bus Bandwidth, DMA Engine, D32 Transfer (Origin/Onyx 2<br>Systems) 106 |

| Table A-1 | Summary of Frame Scheduler Example Programs 131                            |

#### **About This Guide**

A real-time program is one that must maintain a fixed timing relationship to external hardware. In order to respond to the hardware quickly and reliably, a real-time program must have special support from the system software and hardware.

This guide describes the real-time facilities of IRIX, called REACT, as well as the optional REACT/Pro extensions.

This guide is designed to be read online, using IRIS InSight. You are encouraged to read it in non-linear order using all the navigation tools that Insight provides. In the online book, the name of a reference page ("man page") is red in color (for example, mpin(2) and sproc(2)). You can click on these names to cause the reference page to open automatically in a separate terminal window.

#### Who This Guide Is For

This guide is written for real-time programmers. You, a real-time programmer, are assumed to be

- an expert in the use of your programming language, which must be either C, Ada, or FORTRAN to use the features described here

- knowledgeable about the hardware interfaces used by your real-time program

- familiar with system-programming concepts such as interrupts, device drivers, multiprogramming, and semaphores

You are not assumed to be an expert in UNIX system programming, although you do need to be familiar with UNIX as an environment for developing software.

#### What the Book Contains

Here is a summary of what you will find in the following chapters.

Chapter 1, "Real-Time Programs," describes the important classes of real-time programs, emphasizing the different kinds of performance requirements they have.

Chapter 2, "How IRIX and REACT/Pro Support Real-Time Programs," gives an overview of the real-time features of IRIX. From these survey topics you can jump to the detailed topics that interest you most.

Chapter 3, "Controlling CPU Workload," describes how you can isolate a CPU and dedicate almost all of its cycles to your program's use.

Chapter 4, "Using the Frame Scheduler," describes the REACT/Pro Frame Scheduler, which gives you a simple, direct way to structure your real-time program as a group of cooperating processes, efficiently scheduled on one or more isolated CPUs.

Chapter 5, "Optimizing Disk I/O for a Real-Time Program," describes how to set up disk I/O to meet real-time constraints, including the use of asynchronous I/O and guaranteed-rate I/O.

Chapter 6, "Managing Device Interactions," summarizes the software interfaces to external hardware, including user-level programming of external interrupts and VME and SCSI devices.

Chapter 7, "Managing User-Level Interrupts," describes the user-level interrupt (ULI) facility to perform programmed I/O (PIO) from user space. You can use PIO to initiate a device action that leads to a device interrupt, and you can intercept and handle the interrupt in your program.

Appendix A, "Sample Programs," provides the location of the sample programs that are distributed with the REACT/Pro Frame Scheduler and describes them in detail.

#### Other Useful Books and Sites

The following books contain more information that can be useful to a real-time programmer.

- For a survey of all IRIX facilities and manuals, see *Programming on Silicon Graphics Systems: An Overview*; part number 007-2476-nnn.

- The *IRIXview User's Guide*, part number 007-2824-nnn, tells how to use a graphical performance analysis tool that can be of great help in debugging and tuning a real-time application on a multiprocessor system.

- *Topics in IRIX Programming*, part number 007-2478-nnn, covers several programming facilities only touched on in this book.

- MIPS Compiling and Performance Tuning Guide, 007-2479-nnn covers compiler use.

- The IRIX Device Driver Programmer's Guide, part number 007-0911-nnn, gives details

on all types of device control, including programmed I/O (PIO) and direct memory

access (DMA) from the user process, as well as discussing the design and

construction of device drivers and other kernel-level modules.

- Administration of a multiprocessor is covered in a family of six books, including

- IRIX Admin: System Configuration and Operation (007-2859-nnn)

- IRIX Admin: Disks and Filesystems (007-2825-nnn)

- IRIX Admin: Peripheral Devices (007-2861-nnn)

- For details of the architecture of the CPU, processor cache, processor bus, and virtual memory, see the MIPS R4000 Microprocessor User's Manual, 2nd Ed. by Joseph Heinrich. This and other chip-specific documents are available for downloading from the MIPS home page, http://www.mips.com.

- For programming inter-computer connections using sockets, *IRIX Network Programming Guide*, part number 007-0810-nnn.

- For coding functions in assembly language, MIPSpro Assembly Language Programmer's Guide, part number 007-2418-nnn.

- For information about the physical description of the XIO-VME option for Origin and Onyx 2 systems, refer to the *Origin 2000 and Onyx 2 VME Option Owner's Guide*.

- For information about the SGI Origin 3000 series and Onyx 3000 series, see the following site:

http:/www.sgi.com/origin/3000

In addition, Silicon Graphics offers training courses in Real-Time Programming and in Parallel Programming.

#### **Reader Comments**

If you have comments about the technical accuracy, content, or organization of this document, please tell us. Be sure to include the title and document number of the manual with your comments. (Online, the document number is located in the front matter of the manual. In printed manuals, the document number can be found on the back cover.)

You can contact us in any of the following ways:

• Send e-mail to the following address:

```

techpubs@sgi.com

```

• Use the Feedback option on the Technical Publications Library World Wide Web page:

```

http://techpubs.sgi.com

```

- Contact your customer service representative and ask that an incident be filed in the SGI incident tracking system.

- Send mail to the following address:

Technical Publications SGI 600 Amphitheatre Pkwy., M/S 535 Mountain View, California 94043-1351

• Send a fax to the attention of "Technical Publications" at +1 650 932 0801.

We value your comments and will respond to them promptly.

### Real-Time Programs

This chapter surveys the categories of real-time programs, and indicates which types can best be supported by REACT and REACT/Pro. As an experienced programmer of real-time applications, you might want to read the chapter to verify that this book uses terminology that you know; or you might want to proceed directly to Chapter 2, "How IRIX and REACT/Pro Support Real-Time Programs."

#### **Defining Real-Time Programs**

A real-time program is any program that must maintain a fixed, absolute timing relationship with an external hardware device.

Normal-time programs do not require a fixed timing relationship to external devices. A normal-time program is a correct program when it produces the correct output, no matter how long that takes. You can specify performance goals for a normal-time program, such as "respond in at most 2 seconds to 90% of all transactions," but if the program does not meet the goals, it is merely slow, not incorrect.

A real-time program is one that is incorrect and unusable if it fails to meet its performance requirements, and so falls out of step with the external device.

#### **Examples of Real-Time Applications**

Some examples of real-time applications include simulators, data collection systems, and process control systems. This section describes each type briefly. Simulators and data collection systems are described in more detail in following sections.

- A simulator maintains an internal model of the world. It receives control inputs, updates the model to reflect them, and displays the changed model. It must process inputs in real time in order to maintain an accurate simulation, and it must generate output in real time to keep up with the display hardware.

- Silicon Graphics systems are well suited to programming many kinds of simulators.

- A data collection system receives input from reporting devices, for example, telemetry receivers, and stores the data. It may be required to process, reduce, analyze or compress the data before storing it. It must react in real time to avoid losing data.

- Silicon Graphics systems are suited to many data collection tasks.

- A process control system monitors the state of an industrial process and constantly

adjusts it for efficient, safe operation. It must react in real time to avoid waste,

damage, or hazardous operating conditions.

- Silicon Graphics systems are suited for many process control applications.

#### **Simulators**

All simulators have the same four components,

- An internal model of the world, or part of it; for example, a model of a vehicle traveling through a model geography, or a model of the physical state of a nuclear power plant.

- External devices to display the state of the model; for example, one or more video displays, audio speakers, or a simulated instrument panel.

- External devices to supply control inputs; for example, a steering wheel, a joystick, or simulated knobs and dials.

- An operator (or hardware under test) that "closes the loop" by moving the controls in response to what is shown on the display.

#### Requirements on Simulators

The real-time requirements on a simulator vary depending on the nature of these four components. Two key performance requirements on a simulator are *frame rate* and *transport delay*.

#### **Frame Rate**

A crucial measure of simulator performance is the rate at which it updates the display. This rate is called the frame rate, whether or not the simulator displays its model on a video screen.

Frame rate is given in cycles per second (abbreviated Hz). Typical frame rates run from 15 Hz to 60 Hz, although rates higher and lower than these are used in special situations.

The inverse of frame rate is *frame interval*. For example, a frame rate of 60 Hz implies a frame interval of 1/60 second, or 16.67 milliseconds. To maintain a frame rate of 60 Hz, a simulator must update its model and prepare a new display in less than 16.67 ms.

The REACT/Pro Frame Scheduler (FRS) helps you organize a multiprocess application to achieve a specified frame rate. (See Chapter 4, "Using the Frame Scheduler.")

#### **Transport Delay**

Transport delay is the term for the number of frames that elapses before a control motion is reflected in the display. When the transport delay is too long, the operator perceives the simulation as sluggish or unrealistic. If a visual display lags behind control inputs, a human operator can become physically ill.

#### **Aircraft Simulators**

Simulators for real or hypothetical aircraft or spacecraft typically require frame rates of 30 Hz to 120 Hz and transport delays of 1 or 2 frames. There can be several analogue control inputs or and possibly many digital control inputs (simulated switches and circuit breakers, for example). There are often multiple video display outputs (one each for the left, forward and right "windows"), and possibly special hardware to shake or tilt the "cockpit." The display in the "windows" must have a convincing level of detail.

Silicon Graphics systems with REACT/Pro are well suited to building aircraft simulators.

#### **Ground Vehicle Simulators**

Simulators for automobiles, tanks, and heavy equipment have been built with Silicon Graphics systems. Frame rates and transport delays are similar to those for aircraft simulators. However, there is a smaller world of simulated "geography" to maintain in the model. Also, the viewpoint of the display changes more slowly, and through smaller angles, than the viewpoint from an aircraft simulator. These factors can make it somewhat simpler for a ground vehicle simulator to update its display.

#### **Plant Control Simulators**

A simulator can be used to train the operators of an industrial plant such as a nuclear or conventional power generation plant. Power-plant simulators have been built using Silicon Graphics systems.

The frame rate of a plant control simulator can be as low as 1 or 2 Hz. However, the number of control inputs (knobs, dials, valves, and so on) can be very large. Special hardware may be required to attach the control inputs and multiplex them onto the VME or PCI bus. Also, the number of display outputs (simulated gauges, charts, warning lights, and so on) can be very large and may also require custom hardware to interface them to the computer.

#### Virtual Reality Simulators

A virtual reality simulator aims to give its operator a sense of presence in a computer-generated world. (So does a vehicle simulator. One difference is that a vehicle simulator strives for an exact model of the laws of physics, which a virtual reality simulator typically does not need to do.)

Usually the operator can see only the simulated display, and has no other visual referents. Because of this, the frame rate must be high enough to give smooth, nonflickering animation, and any perceptible transport delay can cause nausea and disorientation. However, the virtual world is not required (or expected) to look like the real world, so the simulator may be able to do less work to prepare the display.

Silicon Graphics systems, with their excellent graphic and audio capabilities, are well suited to building virtual reality applications.

#### Hardware-in-the-Loop Simulators

The operator of a simulator need not be a person. In a hardware-in-the-loop (HITL) simulator, the role of operator is played by another computer, such as an aircraft autopilot or the control and guidance computer of a missile. The inputs to the computer under test are the simulator's display output. The output signals of the computer under test are the simulator's control inputs.

Depending on the hardware being exercised, the simulator may have to maintain a very high frame rate, up to several thousand hertz. Silicon Graphics systems are excellent choices for HITL simulators.

#### **Data Collection Systems**

A data collection system has the following major parts:

- 1. Sources of data, for example telemetry. Often the source or sources are interfaced to the VME bus, but the PCI bus, serial ports, SCSI devices, and other device types are also used.

- 2. A repository for the data. This can be a raw device such as a tape, or it can be a disk file or even a database system.

- 3. Rules for processing. The data collection system might be asked only to buffer the data and copy it to disk. Or it might be expected to compress the data, smooth it, sample it, or filter it for noise.

- 4. Optionally, a display. The data collection system may be required to display the status of the system or to display a summary or sample of the data. The display is typically not required to maintain a particular frame rate, however.

#### Requirements on Data Collection Systems

The first requirement on a data collection system is imposed by the *peak data rate* of the combined data sources. The system must be able to receive data at this peak rate without an *overrun*; that is, without losing data because it could not read the data as fast as it arrived.

The second requirement is that the system must be able to process and write the data to the repository at the *average data rate* of the combined sources. Writing can proceed at the average rate as long as there is enough memory to buffer short bursts at the peak rate.

You might specify a desired frame rate for updating the display of the data. However, there is usually no real-time requirement on display rate for a data collection system. That is, the system is correct as long as it receives and stores all data, even if the display is updated slowly.

#### **Real-Time Programming Languages**

The majority of real-time programs are written in C, which is the most common language for system programming on UNIX. All of the examples in this book are in C syntax.

The second most common real-time language is Ada, which is used for many defense-related projects. Silicon Graphics sells Ada 95, an implementation of the language. Ada 95 programs can call any function that is available to a C program, so all the facilities described in this book are available, although the calling syntax may vary slightly. Ada offers additional features that are useful in real-time programming; for example, it includes a partial implementation of POSIX threads, which is used to implement Ada tasking.

Some real-time programs are written in FORTRAN. A program in FORTRAN can access any IRIX system function, that is, any facility that is specified in section 2 of the reference pages. For example, all the facilities of the REACT/Pro Frame Scheduler are accessible through the IRIX system function **schedctl()**, and hence can be accessed from a FORTRAN program (see "The Frame Scheduler API" on page 48).

A FORTRAN program cannot directly call C library functions, so any facility that is documented in volume 3 of the reference pages is not directly available in FORTRAN. Thus the **mmap()** function, a system function, is available, but the **usinit()** library function, which is basic to SGI semaphores and locks, is not available. However, it is possible to link subroutines in C to FORTRAN programs, so you can write interface subroutines to encapsulate C library functions and make them available to a FORTRAN program.

## How IRIX and REACT/Pro Support Real-Time Programs

This chapter provides an overview of the real-time support for programs in IRIX and REACT/Pro.

Some of the features mentioned here are discussed in more detail in the following chapters of this guide. For details on other features, you are referred to reference pages or to other manuals. The main topics surveyed are:

- "Kernel Facilities for Real-Time Programs," including special scheduling disciplines, isolated CPUs, and locked memory pages

- "REACT/Pro Frame Scheduler," which takes care of the details of scheduling multiple threads on multiple CPUs at guaranteed rates

- "Synchronization and Communication," reviewing the ways that a concurrent, multi-threaded program can coordinate its work

- "Timers and Clocks," reviewing your options for time-stamping and interval timing

- "Interchassis Communication," reviewing two ways of connecting multiple chassis

#### **Kernel Facilities for Real-Time Programs**

The IRIX kernel has a number of features that are valuable when you are designing your real-time program.

#### **Kernel Optimizations**

The IRIX kernel has been optimized for performance in a multiprocessor environment. Some of the optimizations are as follows:

- Instruction paths to system calls and traps are optimized, including some hand coding, to maximize cache utilization.

- In the real-time dispatch class (described further in "Using Priorities and Scheduling Queues" on page 19), the run queue is kept in priority-sorted order for fast dispatching.

- Floating point registers are saved only if the next process needs them, and restored only if saved.

- The kernel tries to redispatch a process on the same CPU where it most recently ran, looking for some of its data remaining in cache (see "Understanding Affinity Scheduling" on page 24).

#### **Special Scheduling Disciplines**

The default IRIX scheduling algorithm is designed to ensure fairness among time-shared users. Called an "earnings-based" scheduler, the kernel credits each process group with a certain number of microseconds on each dispatch cycle. The process with the fattest "bank account" is dispatched first. If a process exhausts its "bank account" it is preempted.

#### **POSIX Real-Time Policies**

While the earnings-based scheduler is effective at scheduling timeshare applications, it is not suitable for real-time. For deterministic scheduling, IRIX provides the POSIX real-time policies: first-in-first-out and round robin. These policies share a real-time priority band consisting of 256 priorities. Processes scheduled using the POSIX real-time policies are not subject to "earnings" controls. For more information about scheduling, see "Understanding the Real-Time Priority Band" on page 21 and the realtime(5) reference page.

#### **Gang Scheduling**

When your program is structured as a share process group (using **sproc()**), you can request that all the processes of the group be scheduled as a "gang." The kernel runs all the members of the gang concurrently, provided there are enough CPUs available to do so. This helps to ensure that, when members of the process group coordinate through the use of locks, a lock is usually be released in a timely manner. Without gang scheduling, the process that holds a lock may not be scheduled in the same interval as another process that is waiting on that lock.

For more information, see "Using Gang Scheduling" on page 25.

#### **Locking Virtual Memory**

IRIX allows a process to lock all or part of its virtual memory into physical memory, so that it cannot be paged out and a page fault cannot occur while it is running.

Memory linking prevents unpredictable delays caused by paging. Of course the locked memory is not available for the address spaces of other processes. The system must have enough physical memory to hold the locked address space and space for a minimum of other activities.

The system calls used to lock memory, such as **mlock()** and **mlockall()**, are discussed in detail in *Topics in IRIX Programming* (see "Other Useful Books and Sites" on page xix).

#### **Mapping Processes and CPUs**

Normally IRIX tries to keep all CPUs busy, dispatching the next ready process to the next available CPU. (This simple picture is complicated by the needs of affinity scheduling, and gang scheduling). Since the number of ready processes changes all the time, dispatching is a random process. A normal process cannot predict how often or when it will next be able to run. For normal programs this does not matter, as long as each process continues to run at a satisfactory average rate.

Real-time processes cannot tolerate this unpredictability. To reduce it, you can dedicate one or more CPUs to real-time work. There are two steps:

- Restrict one or more CPUs from normal scheduling, so that they can run only the processes that are specifically assigned to them.

- Assign one or more processes to run on the restricted CPUs.

A process on a dedicated CPU runs when it needs to run, delayed only by interrupt service and by kernel scheduling cycles (if scheduling is enabled on that CPU). For details, see "Assigning Work to a Restricted CPU" on page 33. The REACT/Pro Frame Scheduler takes care of both steps automatically; see "REACT/Pro Frame Scheduler" on page 11.

#### **Controlling Interrupt Distribution**

In normal operations, CPUs receive frequent interrupts:

- I/O interrupts from devices attached to, or near, that CPU.

- A scheduling clock causes an interrupt to every CPU every time-slice interval of 10 milliseconds.

- Whenever interval timers expire ("Timers and Clocks" on page 16), a CPU handling timers receives timer interrupts.

- When the map of virtual to physical memory changes, a TLB interrupt is broadcast to all CPUs.

These interrupts can make the execution time of a process unpredictable. However, you can designate one or more CPUs for real-time use, and keep interrupts of these kinds away from those CPUs. The system calls for interrupt control are discussed further in "Minimizing Overhead Work" on page 27. The REACT/Pro Frame Scheduler also takes care of interrupt isolation.

#### **REACT/Pro Frame Scheduler**

Many real-time programs must sustain a fixed frame rate. In such programs, the central design problem is that the program must complete certain activities during every frame interval.

The REACT/Pro Frame Scheduler (FRS) is a process execution manager that schedules activities on one or more CPUs in a predefined, cyclic order. The scheduling interval is determined by a repetitive time base, usually a hardware interrupt.

The Frame Scheduler makes it easy to organize a real-time program as a set of independent, cooperating threads. The Frame Scheduler manages the housekeeping details of reserving and isolating CPUs. You concentrate on designing the activities and implementing them as threads in a clean, structured way. It is relatively easy to change the number of activities, or their sequence, or the number of CPUs, even late in the project. For detailed information about the Frame Scheduler, see Chapter 4, "Using the Frame Scheduler."

#### **Synchronization and Communication**

In a program organized as multiple, cooperating processes, the processes need to share data and coordinate their actions in well-defined ways. IRIX with REACT provides the following mechanisms, which are surveyed in the topics that follow:

- Shared memory allows a single segment of memory to appear in the address spaces of multiple processes.

- Semaphores are used to coordinate access from multiple processes to resources that they share.

- Locks provide a low-overhead, high-speed method of mutual exclusion.

- Barriers make it easy for multiple processes to synchronize the start of a common activity.

- Signals provide asynchronous notification of special events or errors. IRIX supports signal semantics from all major UNIX heritages, but POSIX-standard signals are recommended for real-time programs.

#### **Shared Memory Segments**

IRIX allows you to map a segment of memory into the address spaces of two or more processes at once. The block of shared memory can be read concurrently, and possibly written, by all the processes that share it. IRIX supports the POSIX and the SVR4 models of shared memory, as well as a system of shared arenas unique to IRIX. These facilities are covered in detail in *Topics in IRIX Programming* (see "Other Useful Books and Sites" on page xix).

#### **Semaphores**

A semaphore is a flexible synchronization mechanism used to signal an event, limit concurrent access to a resource, or enforce mutual exclusion of critical code regions.

IRIX implements industry standard POSIX and SVR4 semaphores, as well as its own arena-based version. All three versions are discussed in *Topics in IRIX Programming* (see "Other Useful Books and Sites" on page xix). While the interfaces and semantics of each type are slightly different, the way they are used is fundamentally the same.

Semaphores have two primary operations that allow threads to atomically increment or decrement the value of a semaphore. With POSIX semaphores, these operations are **sem\_post()** and **sem\_wait()**, respectively (see sem\_post(3) and sem\_wait(3) for additional information).

When a thread decrements a semaphore and causes its value to becomes less than zero, the thread blocks; otherwise, the thread continues without blocking. A thread blocked on a semaphore typically remains blocked until another thread increments the semaphore.

The wakeup order depends on the version of semaphore being used:

POSIX Thread with the highest priority waiting for the longest amount of time

(priority-based)

Arena Process waiting the longest amount of time (FIFO-based)

SVR4 Process waiting the longest amount of time (FIFO-based)

**Tip:** Silicon Graphics recommends using the POSIX semaphores for the synchronization of real-time threads, because they queue blocked threads in priority order and outperform the other semaphore versions with low to no contention.

Following are examples of using semaphores.

- To implement a lock using POSIX semaphores, an application initializes a semaphore to 1, and uses sem\_wait() to acquire the semaphore and sem\_post() to release it.

- To use semaphores for event notification, an application initializes the semaphore to

0. Threads waiting for the event to occur call sem\_wait(), while threads signaling

the event use sem\_post().

#### Locks

A lock is a mutually exclusive synchronization object that represents a shared resource. A process that wants to use the resource sets a lock and later releases the lock when it is finished using the resource.

As discussed in "Semaphores" on page 12, a lock is functionally the same as a semaphore that has a count of 1. The set-lock operation acquires a lock for exclusive use of a resource. On a multiprocessor system, one important difference between a lock and semaphore is when a resource is not immediately available, a semaphore always blocks the process, while a lock causes a process to spin until the resource becomes available.

A lock, on a multiprocessor system, is set by "spinning." The program enters a tight loop using the test-and-set machine instruction to test the lock's value and to set it as soon as the lock is clear. In practice the lock is often already available, and the first execution of test-and-set acquires the lock. In this case, setting the lock takes a trivial amount of time.

When the lock is already set, the process spins on the test a certain number of times. If the process that holds the lock is executing concurrently in another CPU, and if it releases the lock during this time, the spinning process acquires the lock instantly. There is zero latency between release and acquisition, and no overhead from entering the kernel for a system call.

If the process has not acquired the lock after a certain number of spins, it defers to other processes by calling **sginap()**. When the lock is released, the process resumes execution.

For more information on locks, refer to *Topics in IRIX Programming* (see "Other Useful Books and Sites" on page xix), and to the usnewlock(3), ussetlock(3), and usunsetlock(3) reference pages.

#### **Mutual Exclusion Primitives**

IRIX supports library functions that perform atomic (uninterruptible) sample-and-set operations on words of memory. For example, **test\_and\_set()** copies the value of a word and stores a new value into the word in a single operation; while **test\_then\_add()** samples a word and then replaces it with the sum of the sampled value and a new value.

These primitive operations can be used as the basis of mutual-exclusion protocols using words of shared memory. For details, see the test\_and\_set(3p) reference page.

The test\_and\_set() and related functions are based on the MIPS R4000 instructions Load Linked and Store Conditional. Load Linked retrieves a word from memory and tags the processor data cache "line" from which it comes. The following Store Conditional tests the cache line. If any other processor or device has modified that cache line since the Load Linked was executed, the store is not done. The implementation of test\_then\_add() is comparable to the following assembly-language loop:

```

1:

ll retreg, offset(targreg)

add tmpreg, retreg, valreg

sc tmpreg, offset(targreg)

beq tmpreg, 0, b1

```

The loop continues trying to load, augment, and store the target word until it succeeds. Then it returns the value retrieved. For more details on the R4000 machine language, see one of the books listed in "Other Useful Books and Sites" on page xix.

The Load Linked and Store Conditional instructions operate only on memory locations that can be cached. Uncached pages (for example, pages implemented as reflective shared memory, see "Reflective Shared Memory" on page 18) cannot be set by the test\_and\_set() function.

#### **Signals**

A signal is a notification of an event, sent asynchronously to a process. Some signals originate from the kernel: for example, the SIGFPE signal that notifies of an arithmetic overflow; or SIGALRM that notifies of the expiration of a timer interval (for the complete list, see the signal(5) reference page). The Frame Scheduler issues signals to notify your program of errors or termination. Other signals can originate within your own program.

#### **Signal Latency**

The time that elapses from the moment a signal is generated until your signal handler begins to execute is known as *signal latency*. Signal latency can be long (as real-time programs measure time) and signal latency has a high variability. (Some of the factors are discussed under "Signal Delivery and Latency" on page 76.) In general, use signals only to deliver infrequent messages of high priority. Do not use the exchange of signals as the basis for scheduling in a real-time program.

**Note:** Signals are delivered at particular times when using the Frame Scheduler. See "Using Signals Under the Frame Scheduler" on page 76.

#### **Signal Families**

In order to receive a signal, a process must establish a signal handler, a function that is entered when the signal arrives.

There are three UNIX traditions for signals, and IRIX supports all three. They differ in the library calls used, in the range of signals allowed, and in the details of signal delivery (see Table 2-1). Real-time programs should use the POSIX interface for signals.

**Table 2-1** Signal Handling Interfaces

| Function                            | SVR4-compatible Calls     | BSD 4.2 Calls                | POSIX Calls                                                      |

|-------------------------------------|---------------------------|------------------------------|------------------------------------------------------------------|

| set and query<br>signal handler     | sigset(2)<br>signal(2)    | sigvec(3)<br>signal(3)       | sigaction(2)<br>sigsetops(3)<br>sigaltstack(2)                   |

| send a signal                       | sigsend(2)<br>kill(2)     | kill(3)<br>killpg(3)         | sigqueue(2)                                                      |

| temporarily block specified signals | sighold(2)<br>sigrelse(2) | sigblock(3)<br>sigsetmask(3) | sigprocmask(2)                                                   |

| query pending signals               |                           |                              | sigpending(2)                                                    |

| wait for a signal                   | sigpause(2)               | sigpause(3)                  | sigsuspend(2)<br>sigwait(2)<br>sigwaitinfo(2)<br>sigtimedwait(2) |

The POSIX interface supports the following 64 signal types:

| 1-31  | Same as BSD                                   |

|-------|-----------------------------------------------|

| 32    | Reserved by IRIX kernel                       |

| 33-48 | Reserved by the POSIX standard for system use |

| 49-64 | Reserved by POSIX for real-time programming   |

Signals with smaller numbers have priority for delivery. The low-numbered BSD-compatible signals, which include all kernel-produced signals, are delivered ahead of real-time signals; and signal 49 takes precedence over signal 64. (The BSD-compatible interface supports only signals 1-31. This set includes two user-defined signals.)

IRIX supports POSIX signal handling as specified in IEEE 1003.1b-1993. This includes FIFO queueing new signals when a signal type is held, up to a system maximum of queued signals. (The maximum can be adjusted using *systune*; see the systune(1) reference page.)

For more information on the POSIX interface to signal handling, refer to *Topics in IRIX Programming* and to the signal(5), sigaction(2), and sigqueue(2) reference pages.

#### Timers and Clocks

A real-time program sometimes needs a source of timer interrupts, and some need a way to create a high-precision timestamp. Both of these are provided by IRIX. IRIX supports the POSIX clock and timer facilities as specified in IEEE 1003.1b-1993, as well as the BSD itimer facility. The timer facilities are covered in *Topics in IRIX Programming*.

#### **Hardware Cycle Counter**

The hardware cycle counter is a high-precision hardware counter that is updated continuously. The precision of the cycle counter depends on the system in use, but in most, it is a 64-bit counter.

You sample the cycle counter by calling the POSIX function **clock\_gettime()** specifying the CLOCK\_SGI\_CYCLE clock type.

The frequency with which the cycle counter is incremented also depends on the hardware system. You can obtain the resolution of the clock by calling the POSIX function clock\_getres().

**Note:** The cycle counter is synchronyzed only to the CPU crystal and is not intended as a perfect time standard. If you use it to measure intervals between events, be aware that it can drift by as much as 100 microseconds per second, depending on the hardware system in use.

### Interchassis Communication

Silicon Graphics systems support three methods for connecting multiple computers:

- Standard network interfaces let you send packets or streams of data over a local network or the Internet.

- Reflective shared memory (provided by third-party manufacturers) lets you share segments of memory between computers, so that programs running on different chassis can access the same variables.

- External interrupts let one CHALLENGE/Onyx/Origin system signal another.

# **Socket Programming**

One standard, portable way to connect processes in different computers is to use the BSD-compatible socket I/O interface. You can use sockets to communicate within the same machine, between machines on a local area network, or between machines on different continents.

For more information about socket programming, refer to one of the networking books listed in "Other Useful Books and Sites" on page xix.

# Message-Passing Interface (MPI)

The Message-Passing Interface (MPI) is a standard architecture and programming interface for designing distributed applications. Silicon Graphics, Inc., supports MPI in the POWER CHALLENGE Array product. For the MPI standard, see http://www.mcs.anl.gov/mpi/index.html.

The performance of both sockets and MPI depends on the speed of the underlying network. The network that connects nodes (systems) in an Array product has a very high bandwidth.

# **Reflective Shared Memory**

Reflective shared memory consists of hardware that makes a segment of memory appear to be accessible from two or more computer chassis. Actually the CHALLENGE/Onyx implementation consists of VME bus devices in each computer, connected by a very high-speed, point-to-point network.

The VME bus address space of the memory card is mapped into process address space. Firmware on the card handles communication across the network, so as to keep the memory contents of all connected cards consistent. Reflective shared memory is slower than real main memory but faster than socket I/O. Its performance is essentially that of programmed I/O to the VME bus, which is discussed under "PIO Access" on page 102.

Reflective shared memory systems are available for Silicon Graphics equipment from several third-party vendors. The details of the software interface differ with each vendor. However, in most cases you use **mmap()** to map the shared segment into your process's address space (see *Topics in IRIX Programming* as well as the usrvme(7) reference page).

### **External Interrupts**

The Origin/CHALLENGE/Onyx systems support external interrupt lines for both incoming and outgoing external interrupts. Software support for these lines is described in the *IRIX Device Driver Programmer's Guide* and the ei(7) reference page. You can use the external interrupt as the time base for the Frame Scheduler. In that case, the Frame Scheduler manages the external interrupts for you. (See "Selecting a Time Base" on page 59.)

# Controlling CPU Workload

This chapter describes how to use IRIX kernel features to make the execution of a real-time program predictable. Each of these features works in some way to dedicate hardware to your program's use, or to reduce the influence of unplanned interrupts on it. The main topics covered are:

- "Using Priorities and Scheduling Queues" describes scheduling concepts, setting real-time priorities, and affinity and gang scheduling.

- "Minimizing Overhead Work" on page 27 discusses how to remove all unnecessary interrupts and overhead work from the CPUs that you want to use for real-time programs.

- "Minimizing Interrupt Response Time" on page 37 discusses the components of interrupt response time and how to minimize them.

# **Using Priorities and Scheduling Queues**

The default IRIX scheduling algorithm is designed for a conventional time-sharing system, where the best results are obtained by favoring I/O-bound processes and discouraging CPU-bound processes. However, IRIX supports a variety of scheduling disciplines that are optimized for parallel processes. You can take advantage of these in different ways to suit the needs of different programs.

**Note:** You can use the methods discussed here to make a real-time program more predictable. However, to reliably achieve a high frame rate, you should plan to use the REACT/Pro Frame Scheduler described in Chapter 4.

# **Scheduling Concepts**

In order to understand the differences between scheduling methods you need to know some basic concepts.

### **Tick Interrupts**

In normal operation, the kernel pauses to make scheduling decisions every 10 milliseconds in every CPU. The duration of this interval, which is called the "tick" because it is the metronomic beat of the scheduler, is defined in *sys/param.h.* Every CPU is normally interrupted by a timer every tick interval. (However, the CPUs in a multiprocessor are not necessarily synchronized. Different CPUs may take tick interrupts at a different times.)

During the tick interrupt the kernel updates accounting values, does other housekeeping work, and chooses which process to run next—usually the interrupted process, unless a process of superior priority has become ready to run. The tick interrupt is the mechanism that makes IRIX scheduling "preemptive"; that is, it is the mechanism that allows a high-priority process to take a CPU away from a lower-priority process.

Before the kernel returns to the chosen process, it checks for pending signals, and may divert the process into a signal handler.

You can stop the tick interrupt in selected CPUs in order to keep these interruptions from interfering with real-time programs—see "Making a CPU Nonpreemptive" on page 35.

### **Time Slices**

Each process has a guaranteed time slice, which is the amount of time it is normally allowed to execute without being preempted. By default the time slice is 10 ticks, or 100 ms, on a multiprocessor system and 2 ticks, or 20 ms, on a uniprocessor system. A typical process is usually blocked for I/O before it reaches the end of its time slice.

At the end of a time slice, the kernel chooses which process to run next on the same CPU based on process priorities. When runnable processes have the same priority, the kernel runs them in turn.

### Understanding the Real-Time Priority Band

A real-time thread can select one of a range of 256 priorities (0-255) in the real-time priority band, using POSIX interfaces **sched\_setparam()** or **sched\_setscheduler()**. The higher the numeric value of the priority, the more important the thread. The range of priorities is shown in Figure 3-1.

It is important to consider the needs of the application and how it should interact with the rest of the system before selecting a real-time priority. In making this decision, consider the priorities of the system threads.

IRIX manages system threads to handle kernel tasks, such as paging and interrupts. System daemon threads execute between priority range 90 and 109, inclusive. System device driver interrupt threads execute between priority range 200 and 239, inclusive.

An application can set the priorities of its threads above those of the system threads, but this can adversely affect the behavior of the system. For example, if the disk interrupt thread is blocked by a higher priority user thread, disk data access is delayed until the user thread completes.

Setting the priorities of application threads within or above the system thread range requires an advanced understanding of IRIX system threads and their priorities. The priorities of the IRIX system threads are found in /var/sysgen/mtune/kernel. If necessary, you can change these defaults using systune, although this is not recommended for most users (see the systune(1M) reference page for details).

Many soft real-time applications simply need to execute ahead of time-share applications, so priority range 0 through 89 is best suited. Since time-share applications are not priority scheduled, a thread running at the lowest real-time priority (0) still executes ahead of all time-share applications. At times, however, the operating system briefly promotes time-share threads into the real-time band to handle time-outs and avoid priority inversion. In these special cases, the promoted thread's real-time priority is never boosted higher than 1.

| т   |                                    |     |

|-----|------------------------------------|-----|

| 255 | Reserved for System Use            | 255 |

| 254 | -                                  | 254 |

|     | Hard Real-Time                     | _   |

| 240 |                                    | 240 |

|     |                                    |     |

| 239 |                                    | 239 |

| Sy  | stem Device Driver Interrupt Threa | ds  |

| 200 |                                    | 200 |

| 199 |                                    | 199 |

|     |                                    |     |

|     | Interactive Real-Time              |     |

|     |                                    |     |

| 110 |                                    | 110 |

| 109 |                                    | 109 |

|     | 0 . 5                              |     |

|     | System Daemon Threads              |     |

| 90  |                                    | 90  |

| 89  |                                    | 89  |

|     |                                    |     |

|     |                                    |     |

|     | Soft Real-Time                     |     |

|     |                                    |     |

|     |                                    |     |

| 0   |                                    | 0   |

Figure 3-1 Real-Time Priority Band

**Note:** Applications cannot depend on system services if they are running ahead of system threads, without observing system responsiveness timing guidelines.

Interactive real-time applications (such as digital media) need low latency response times from the operating system, but changing interrupt thread behavior is undesirable. In this case, priority range 110 through and including 199 is the best choice, allowing execution ahead of system daemons but behind interrupt threads. Applications in this range are typically cooperating with a device driver, in which case the correct priority for the application is the priority of the device driver interrupt thread minus 50. If the application is multi-threaded, and multiple priorities are warranted, then priorities of threads should be no greater than the priority of the device driver interrupt thread minus 50. Note that threads running at a higher priority than system daemon threads should never run for more than a few milliseconds at a time, in order to preserve system responsiveness.

Hard real-time applications can use priorities 240 through 254 for the most deterministic behavior and the lowest latencies. However, if threads running at this priority range ever reach the state where they consume 100% of the system's processor cycles, the system becomes completely unresponsive. Threads running at a higher priority than the interrupt threads should never run for more that a few hundred microseconds at a time, to preserve system responsiveness.

Priority 255, the highest real-time priority, should not be used by applications. This priority is reserved for system use to handle timers for urgent real-time applications and kernel debugger interrupts. Applications running at this priority risk hanging the system.

The proprietary IRIX interface for selecting a real-time priority, **schedctl()**, is supported for binary compatibility, but is not the interface of choice. The nondegrading real-time priority range of **schedctl()** is remapped onto the POSIX real-time priority band as priorities 90 through 118, as shown in Table 3-1.

Table 3-1

schedctl() Real-Time Priority Range Remapping

| schedctl() | POSIX |

|------------|-------|

| 39         | 90    |

| 38         | 110   |

| 37         | 111   |

| 36         | 112   |

| 35         | 113   |

| 34         | 114   |

| 33         | 115   |

| 32         | 116   |

| 31         | 117   |

| 30         | 118   |

|            |       |

Notice the large gap between the first two priorities; it preserves the scheduling semantics of **schedctl()** threads and system daemons.

Real-time users are encouraged to use tools such as *par* and *irixview* to observe the actual priorities and dynamic behaviors of all threads on a running system (see the par(1) and irixview(1) reference pages for details).

# **Understanding Affinity Scheduling**

Affinity scheduling is a special scheduling discipline used in multiprocessor systems. You do not have to take action to benefit from affinity scheduling, but you should know that it is done.

As a process executes, it causes more and more of its data and instruction text to be loaded into the processor cache. This creates an "affinity" between the process and the CPU. No other process can use that CPU as effectively, and the process cannot execute as fast on any other CPU.

The IRIX kernel notes the CPU on which a process last ran, and notes the amount of the affinity between them. Affinity is measured on an arbitrary scale.

When the process gives up the CPU—either because its time slice is up or because it is blocked—one of three things can happen to the CPU:

- The CPU runs the same process again immediately.

- The CPU spins idle, waiting for work.

- The CPU runs a different process.

The first two actions do not reduce the process's affinity. But when the CPU runs a different process, that process begins to build up an affinity while simultaneously reducing the affinity of the earlier process.

As long as a process has any affinity for a CPU, it is dispatched only on that CPU if possible. When its affinity has declined to zero, the process can be dispatched on any available CPU. The result of the affinity scheduling policy is that:

- I/O-bound processes, which execute for short periods and build up little affinity, are quickly dispatched whenever they become ready.

- CPU-bound processes, which build up a strong affinity, are not dispatched as quickly because they have to wait for "their" CPU to be free. However, they do not suffer the serious delays of repeatedly "warming up" a cache.

# **Using Gang Scheduling**

You can design a real-time program as a family of cooperating, lightweight processes, created with **sproc()**, sharing an address space. These processes typically coordinate their actions using locks or semaphores ("Synchronization and Communication" on page 11).

When process A attempts to seize a lock that is held by process B, one of two things can happen, depending on whether or not process is B is running concurrently in another CPU.

- If process B is not currently active, process A spends a short time in a "spin loop" and then is suspended. The kernel selects a new process to run. Time passes. Eventually process B runs and releases the lock. More time passes. Finally process A runs and now can seize the lock.

- When process B is concurrently active on another CPU, it typically releases the lock

while process A is still in the spin loop. The delay to process A is negligible, and the

overhead of multiple passes into the kernel and out again is avoided.

In a system with many processes, the first scenario is common even when processes A, B, and their siblings have real-time priorities. Clearly it is better if processes A and B are always dispatched concurrently.

Gang scheduling achieves this. Any process in a share group can initiate gang scheduling. Then all the processes that share that address space are scheduled as a unit, using the priority of the highest-priority process in the gang. IRIX tries to ensure that all the members of the share group are dispatched when any one of them is dispatched.

You initiate gang scheduling with a call to **schedctl()**, as sketched in Example 3-1.

### **Example 3-1** Initiating Gang Scheduling

```

if (-1 == schedctl(SCHEDMODE,SGS_GANG))

{

if (EPERM == errno)

fprintf(stderr,"You forget to suid again\n");

else

perror("schedctl");

}

```

You can turn gang scheduling off again with another call, passing SGS\_FREE in place of SGS\_GANG.

# **Changing the Time Slice Duration**

You can change the length of the time slice for all processes from its default (100 ms, multiprocessor systems/20 ms, uniprocessor systems) using the *systune* command (see the systune(1) reference page). The kernel variable is *slice\_size*; its value is the number of tick intervals that make up a slice. There is probably no good reason to make a global change of the time-slice length.

You can change the length of the time slice for one particular process using the **schedctl()** function (see the schedctl(2) reference page), as shown in Example 3-2.

### **Example 3-2** Setting the Time-Slice Length

```

#include <sys/schedctl.h>

int setMyTimeSliceInTicks(const int ticks)

{

int ret = schedctl(SLICE,0,ticks)

if (-1 == ret)

{ perror("schedctl(SLICE)"); }

return ret;

}

```

You can lengthen the time slice for the parent of a process group that is gang-scheduled (see "Using Gang Scheduling" on page 25). This keeps members of the gang executing concurrently longer.

# Minimizing Overhead Work

A certain amount of CPU time must be spent on general housekeeping. Since this work is done by the kernel and triggered by interrupts, it can interfere with the operation of a real-time process. However, you can remove almost all such work from designated CPUs, leaving them free for real-time work.

First decide how many CPUs are required to run your real-time application (regardless of whether it is to be scheduled normally, or as a gang, or by the Frame Scheduler). Then apply the following steps to isolate and restrict those CPUs. The steps are independent of each other. Each needs to be done to completely free a CPU.

- "Assigning the Clock Processor" on page 27

- "Isolating a CPU From Sprayed Interrupts" on page 28

- "Redirecting Interrupts" on page 28

- "Restricting a CPU From Scheduled Work" on page 30

- "Isolating a CPU From TLB Interrupts" on page 34

- "Making a CPU Nonpreemptive" on page 35

# **Assigning the Clock Processor**

Every CPU that uses normal IRIX scheduling takes a "tick" interrupt that is the basis of process scheduling. However, one CPU does additional housekeeping work for the whole system, on each of its tick interrupts. You can specify which CPU has these additional duties using the privileged *mpadmin* command (see the mpadmin(1) reference page). For example, to make CPU 0 the clock CPU (a common choice), use

```

mpadmin -c 0

```

The equivalent operation from within a program uses **sysmp()** as shown in Example 3-3 (see also the sysmp(2) reference page).

### **Example 3-3** Setting the Clock CPU

```

#include <sys/sysmp.h>

int setClockTo(int cpu)

{

int ret = sysmp(MP_CLOCK,cpu);

if (-1 == ret) perror("sysmp(MP_CLOCK)");

return ret;

}

```

# **Unavoidable Timer Interrupts**

In machines based on the R4x00 CPU, even when the clock and fast timer duties are removed from a CPU, that CPU still gets an unwanted interrupt as a 5-microsecond "blip" every 80 seconds. Systems based on the R8000 and R10000 CPUs are not affected, and processes running under the Frame Scheduler are not affected even by this small interrupt.

# **Isolating a CPU From Sprayed Interrupts**

By default, the Origin, Onyx 2, CHALLENGE, and Onyx systems direct I/O interrupts from the bus to CPUs in rotation (called *spraying interrupts*). You do not want a real-time process interrupted at unpredictable times to handle I/O. The system administrator can isolate one or more CPUs from sprayed interrupts by placing the NOINTR directive in the configuration file /var/sysgen/system/irix.sm. The syntax is

NOINTR cpu# [cpu#]...

Before the NOINTR directive takes effect, the kernel must be rebuilt using the command <code>/etc/autoconfig -vf</code>, and rebooted.

# Redirecting Interrupts

To minimize latency of real-time interrupts, it is often necessary to direct them to specific real-time processors. This process is called interrupt redirection.

A device interrupt can be redirected to a specific processor using the DEVICE\_ADMIN directive in the /usr/sysgen/system/irix.sm file.

The DEVICE\_ADMIN and the NOINTR directives are typically used together to guarantee that the target processor only handles the redirected interrupts.

For example, adding the following lines to the *irix.sm* system configuration file ensures that CPU 1 handles only PCI interrupt 4:

NOINTR 1

DEVICE\_ADMIN: /hw/module/1/slot/io1/baseio/pci/4 INTR\_TARGET=/hw/cpunum/1

On the Origin 3000 series, if a DEVICE\_ADMIN directive is used to redirect an interrupt, the hardware limitations might not allow the the interrupt to be redirected to the requested CPU. If this occurs, you will see the following message on the console and in the system log (*hwgraph* path and CPU number as appropriate for each case):

```

WARNING:Override explicit interrupt targetting: /hw/module/001c10/Ibrick/xtalk/15/pci/4/ei(0x2f8),unable to target CPU 4

```

For a threaded interrupt handler, the directive will still ensure that the interrupt handler thread is given control on the specified CPU.

If the interrupt handler is non-threaded and interrupt redirection is requested to ensure the handler runs on a particular CPU, choice of the interrupt CPU is critical. A device on a particular PCI bus can interrupt CPUs only on one Processor Interface (PI), either PI-0 or PI-1. (A device can still interrupt CPUs on any node, but it can interrupt only those on one PI.) At boot time, it is determined which CPUs are interruptible from which PCI bus. Once determined, the set of interruptible CPUs for a particular PCI bus should not change from boot to boot, unless a system configuration change is made, such as disabling the CPU and reconfiguring the I/O.

If you receive the previously mentioned warning message, indicating that an interrupt redirect failed, you can perform the following procedure to determine to which CPUs an interrupt can be directed, and then change the DEVICE\_ADMIN directive accordingly. From the message, you know that CPU 4 is on a PI that cannot receive interrupts from the device in question. As shown in the following example, output from an *ls* command indicates which PI the CPU is on. In this case, it is PI-0, as indicated by the 0 in the path.

```

o3000%ls -1 /hw/cpumun/4

lrw----- ... 4 -> /hw/module/001c13/node/cpubus/0/a

```

You now know that the PCI bus that this device is on can interrupt CPUs only on PI-1. Using this knowledge and output from the *ls* command, you can choose an interruptible CPU. As shown from the output from the *ls* command in the following example, changing the DEVICE\_ADMIN directive to use CPU 2, 3, 6, or 7 will allow you to work around this hardware limitation.

### 03000%ls -1 /hw/cpunum

# total lrw----- ... 0 -> /hw/module/001c10/node/cpubus/0/a lrw----- ... 1 -> /hw/module/001c10/node/cpubus/0/b lrw----- ... 2 -> /hw/module/001c10/node/cpubus/1/a lrw---- ... 3 -> /hw/module/001c10/node/cpubus/1/b lrw---- ... 4 -> /hw/module/001c13/node/cpubus/0/a

```

lrw----- ... 5 -> /hw/module/001c13/node/cpubus/0/b

lrw---- ... 6 -> /hw/module/001c13/node/cpubus/1/a

lrw---- ... 7 -> /hw/module/001c13/node/cpubus/1/b

```

**Note:** The actual DEVICE\_ADMIN directive varies depending on the system's hardware configuration.

Before the directives take effect, the kernel must be rebuilt using the command <code>/etc/autoconfig -vf</code>, and rebooted.

# **Understanding the Vertical Sync Interrupt**

In systems with dedicated graphics hardware, the graphics hardware generates a variety of hardware interrupts. The most frequent of these is the vertical sync interrupt, which marks the end of a video frame. The vertical sync interrupt can be used by the Frame Scheduler as a time base (see "Vertical Sync Interrupt" on page 60). Certain GL and Open GL functions are internally synchronized to the vertical sync interrupt (for an example, refer to the gsync(3g) reference page).

All the interrupts produced by dedicated graphics hardware are at an inferior priority compared to other hardware. All graphics interrupts including the vertical sync interrupt are directed to CPU 0. They are not "sprayed" in rotation, and they cannot be directed to a different CPU.

### Restricting a CPU From Scheduled Work

For best performance of a real-time process or for minimum interrupt response time, you need to use one or more CPUs without competition from other scheduled processes. You can exert three levels of increasing control: *restricted*, *isolated*, and *nonpreemptive*.

In general, the IRIX scheduling algorithms run a process that is ready to run on any CPU. This is modified by considerations of

- affinity—CPUs are made to execute the processes that have developed affinity to them

- processor group assignments—the *pset* command can force a specified group of CPUs to service only a given scheduling queue

You can *restrict* one or more CPUs from running any scheduled processes at all. The only processes that can use a restricted CPU are processes that you assign to those CPUs.

**Note:** Restricting a CPU overrides any group assignment made with *pset*. A restricted CPU remains part of a group, but does not perform any work you assign to the group using *pset*.

You can find out the number of CPUs that exist, and the number that are still unrestricted, using the **sysmp()** function as in Example 3-4.

### **Example 3-4** Number of Processors Available and Total

```

#include <sys/sysmp.h>

int CPUsInSystem = sysmp(MP_NPROCS);

int CPUsNotRestricted = sysmp(MP_NAPROCS);

```

To restrict one or more CPUs, you can use *mpadmin*. For example, to restrict CPUs 4 and 5, you can use

```

mpadmin -r 4 mpadmin -r 5

```

The equivalent operation from within a program uses **sysmp()** as in Example 3-5 (see also the sysmp(2) reference page).

### **Example 3-5** Restricting a CPU

```

#include <sys/sysmp.h>

int restrictCpuN(int cpu)

{

int ret = sysmp(MP_RESTRICT,cpu);

if (-1 == ret) perror("sysmp(MP_RESTRICT)");

return ret;

}

```

You remove the restriction, allowing the CPU to execute any scheduled process, with *mpadmin -u* or with **sysmp**(MP\_EMPOWER).

**Note:** The following points are important to remember:

- The CPU assigned to handle the scheduling clock ("Assigning the Clock Processor" on page 27) must not be restricted.

- The REACT/Pro Frame Scheduler automatically restricts and isolates any CPU it uses. See Chapter 4.

### Assigning Work to a Restricted CPU

After restricting a CPU, you can assign processes to it using the command *runon* (see the runon(1) reference page). For example, to run a program on CPU 3, you could use

```

runon 3 ~rt/bin/rtapp

```

The equivalent operation from within a program uses **sysmp()** as in Example 3-6 (see also the sysmp(2) reference page).

### **Example 3-6** Assigning the Calling Process to a CPU

```

#include <sys/sysmp.h>

int runMeOn(int cpu)

{

int ret = sysmp(MP_MUSTRUN,cpu);

if (-1 == ret) perror("sysmp(MP_MUSTRUN)");

return ret;

}

```

You remove the assignment, allowing the process to execute on any available CPU, with **sysmp**(MP\_RUNANYWHERE). There is no command equivalent.

The assignment to a specified CPU is inherited by processes created by the assigned process. Thus if you assign a real-time program with *runon*, all the processes it creates run on that same CPU. More often you want to run multiple processes concurrently on multiple CPUs. There are three approaches you can take:

- 1. Use the REACT/Pro Frame Scheduler, letting it restrict CPUs for you.