HD I/O Option Board Owner's Guide

Document Number 007-3968-002

#### **CONTRIBUTORS**

Written by Carolyn Curtis

Illustrated by Cheri Brown, Dan Young, Dany Galgani, and Carolyn Curtis Production by Carlos Miqueo

Engineering contributions by Bill Warner, Ted Marsh, Greg Sadowski, Ed Miszkiewicz, Kirk Knapp, Michael Poimboeuf, and Scott Pritchett

St. Peter's Basilica image courtesy of ENEL SpA and InfoByte SpA. Disk Thrower image courtesy of Xavier Berenguer, Animatica.

© 1999, Silicon Graphics, Inc.— All Rights Reserved

The contents of this document may not be copied or duplicated in any form, in whole or in part, without the prior written permission of Silicon Graphics, Inc.

#### LIMITED AND RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in the Rights in Data clause at FAR 52.227-14 and/or in similar or successor clauses in the FAR, or in the DOD, DOE or NASA FAR Supplements. Unpublished rights reserved under the Copyright Laws of the United States. Contractor/manufacturer is Silicon Graphics, Inc., 1600 Amphitheatre Pkwy., Mountain View, CA 94043-1351.

#### FCC Warning

This equipment has been tested and found compliant with the limits for a Class A digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference at his own expense.

#### Attention

This product requires the use of external shielded cables in order to maintain compliance pursuant to Part 15 of the FCC Rules.

**European Union Statement**

This device complies with the European Directives listed on the "Declaration of Conformity" which is included with each product. The CE mark insignia displayed on the device is an indication of conformity to the aforementioned European requirements.

International Special Committee on Radio Interference (CISPR) This equipment has been tested to and is in compliance with the Class A limits per CISPR publication 22, Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment; Germany's BZT Class A limits for Information Technology Equipment; and Japan's VCCI Class 1 limits.

#### Canadian Department of Communications Statement

This digital apparatus does not exceed the Class A limits for radio noise emissions from digital apparatus as set out in the Radio Interference Regulations of the Canadian Department of Communications.

Attention

Cet appareil numérique n'émet pas de perturbations radioélectriques dépassant les normes applicables aux appareils numériques de Classe A préscrites dans le Règlement sur les interferences radioélectriques etabli par le Ministère des Communications du Canada.

VCCI Class 1 Statement for Japan

この装置は、情報処理装置等電波障害自主規制協議会 (VCCI) の基準に基づくクラス A 情報技術装置です。この装置を家庭環境 で使用すると電波妨害を引き起こすことがあります。この場合に は使用者が適切な対策を講ずるよう要求されることがあります。 Chinese Class A Warning

### 警告使用者:

這是甲類的資訊產品,在居住的環境中使用時,可能會造成射頻 干擾,在這種情況下,使用者會被要求採取某些適當的對策.

Silicon Graphics, SGI, the Silicon Graphics logo, OpenGL, Origin, and IRIS are registered trademarks and IRIX, XIO, Onyx, Onyx2, Origin200, Origin2000, Graphics Library, REACT, RealityEngine, XFS, and Sirius Video are trademarks of Silicon Graphics, Inc.

Philips is a registered trademark and Spirit Datacine is a trademark of Philips Electronics, N.V. D19.

QuickTime is a registered trademark of Apple Computer, Inc.

HD I/O Option Board Owner's Guide Document Number 007-3968-002

# Contents

List of Figures ix

List of Tables xi

About This Guide xiii Audience xiii Structure of This Guide xiii Other Documents xiv Conventions Used in This Guide xv

#### **1.** Features and Capabilities 1

HD I/O Features 1 Supported Video Formats 1 Genlock and Timing Features 2 Other Features 2 HD I/O Panel and Cable 5

#### 2. Programming the HD I/O Option 7

VL Basics for the HD I/O Option Board 7 VL Concepts 8 VL Syntax Elements 9 VL Object Classes 9 VL Nodes for the HD I/O Option 10 VL Data Transfer Functions 12 HD I/O Data Flow 13

HD I/O Controls 14 Setting Controls 15 HD I/O Control Summary 16 VL\_TIMING 19 VL\_FORMAT 20 VL\_PACKING 21 VL\_COLORSPACE 22 VL\_CAP\_TYPE 27 VL\_SIZE and VL\_OFFSET 28 VL\_ZOOM 28 Field Dominance 29 Automatically Correcting for Output Underflow 30 Capturing Graphics to Video 31 HD I/O Events 31 Reporting 32 Examples 32 Capture to Memory for Disk Recording 33 Playback From Memory for Disk Playback 33 Capture to Memory for Graphics 34 3. Synchronizing Data Streams and Signals 35 Using UST, MSC, and Buffered Media Streams for Synchronization 35 Media Library Interfaces for UST and MSC 38 HD I/O Option Board Specifications 39 A. Cable Connectors 40 GPI Interface 44 GPI Connector 44 GPI Transmitter 46 GPI Receiver 47 Genlock 48

| В. | Setting Up the HD I/O Board for Your Video Hardware 49                          |    |

|----|---------------------------------------------------------------------------------|----|

|    | Setting Up Digital Source Video 50                                              |    |

|    | Setting Up the Output (Drain) 52                                                |    |

|    | Setting Up Sync 54                                                              |    |

|    | Setting Up Internal Sync 54                                                     |    |

|    | Setting Up External Sync 55                                                     |    |

|    | Saving Settings 56                                                              |    |

| C. | Pixel Packings and Color Spaces 57                                              |    |

|    | HD I/O Pixel Packings 57                                                        |    |

|    | Packings and Color Spaces 57                                                    |    |

|    | Packing Diagram Conventions 58                                                  |    |

|    | Packings and Library Tokens 60                                                  |    |

|    | Packing Naming Conventions 60                                                   |    |

|    | 16-Bit Pixel Packings 62                                                        |    |

|    | 20-Bit Pixel Packings 63                                                        |    |

|    | 24-Bit Pixel Packings 64                                                        |    |

|    | 32-Bit Pixel Packings 65                                                        |    |

|    | Sampling Patterns 74                                                            |    |

|    | 4:4:4 and 4:4:4:4 Sampling 74                                                   |    |

|    | 4:2:2 and 4:2:2:4 Sampling 75                                                   |    |

| D. | <b>Programming Methods for Real-Time Digital Media Recording and Playback</b> 7 | 77 |

|    | Digital Media Buffers 78                                                        |    |

|    | Direct I/O 78                                                                   |    |

|    | Multiprocessing 80                                                              |    |

|    | Asynchronous I/O 81                                                             |    |

| E. | Installing HD I/O Software on a New Disk 83                                     |    |

e

Index 85

# List of Figures

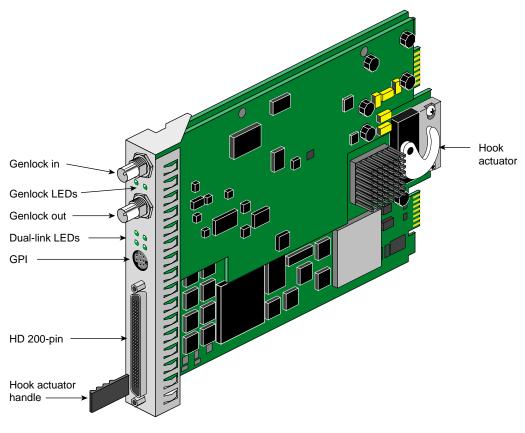

| Figure 1-1 | HD I/O Option Board 3                          |  |  |

|------------|------------------------------------------------|--|--|

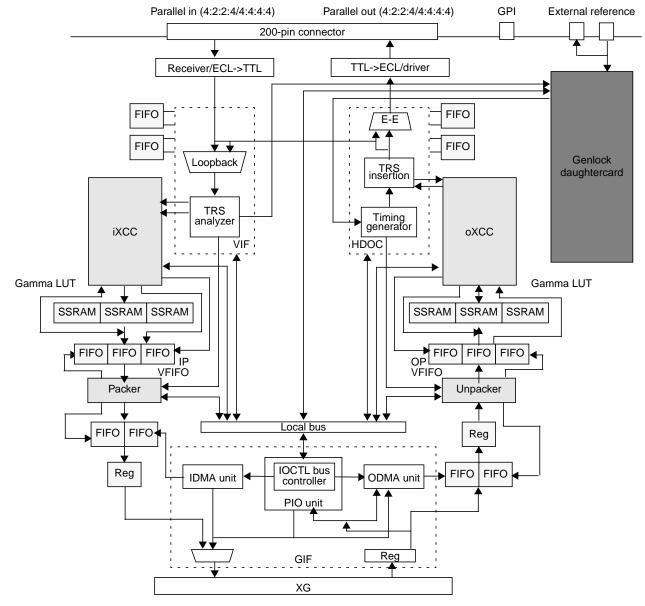

| Figure 1-2 | HD I/O Board Diagram, Simplified 4             |  |  |

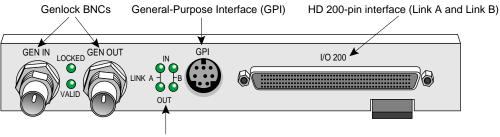

| Figure 1-3 | HD I/O Board Connectors 5                      |  |  |

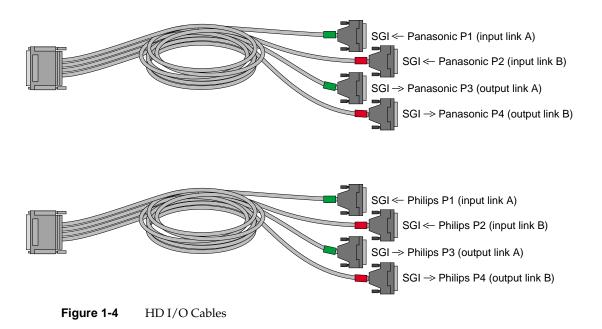

| Figure 1-4 | HD I/O Cables 5                                |  |  |

| Figure 2-1 | Simple VL Path 8                               |  |  |

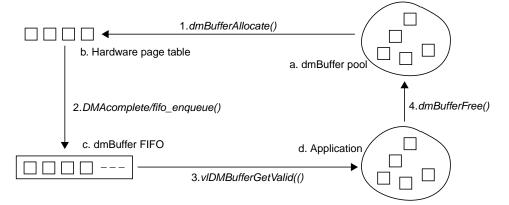

| Figure 2-2 | Data Flow, Input 13                            |  |  |

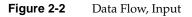

| Figure 2-3 | Data Flow, Output 13                           |  |  |

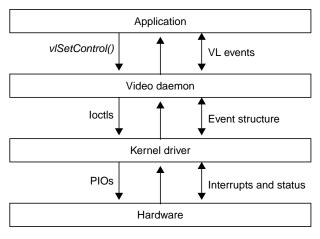

| Figure 2-4 | Control Flow 14                                |  |  |

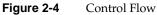

| Figure 2-5 | Color-Space Conversion Example 26              |  |  |

| Figure 2-6 | Fields and Frames for SMPTE 274M 29            |  |  |

| Figure A-1 | HD I/O Cables 40                               |  |  |

| Figure A-2 | GPI Connector 44                               |  |  |

| Figure A-3 | GPI Pinouts 44                                 |  |  |

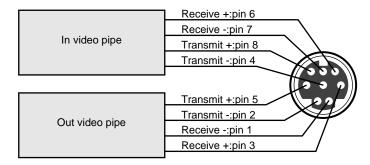

| Figure A-4 | GPI Pins and HD I/O Video Pipes 45             |  |  |

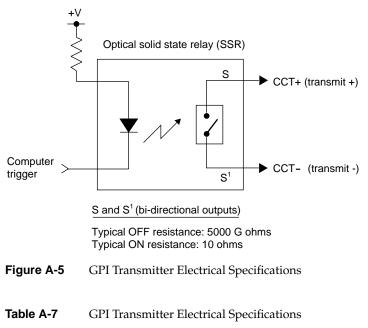

| Figure A-5 | GPI Transmitter Electrical Specifications 46   |  |  |

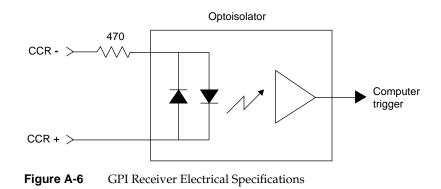

| Figure A-6 | GPI Receiver Electrical Specifications 47      |  |  |

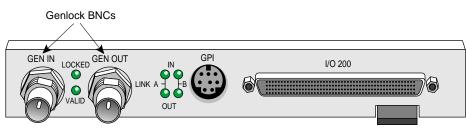

| Figure A-7 | Genlock BNCs 48                                |  |  |

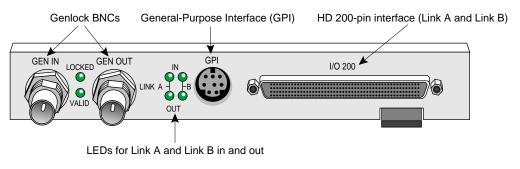

| Figure B-1 | HD I/O Ports 49                                |  |  |

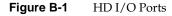

| Figure B-2 | HD I/O Cables 50                               |  |  |

| Figure B-3 | Selecting Digital Input Video Format in vcp 51 |  |  |

| Figure B-4 | Selecting Video Drain Format 53                |  |  |

| Figure B-5 | Setting Standalone or Genlock Sync 54          |  |  |

| Figure C-1 | VL_PACKING_444_8 58                            |  |  |

| Figure C-2 | VL_PACKING_242_8 62                            |  |  |

| Figure C-3 | VL_PACKING_R242_8 62                           |  |  |

| Figure C-4 | VL_PACKING_242_10 63                           |  |  |

| Figure C-5 | VL_PACKING_R242_10 63                          |  |  |

|            |                                                |  |  |

| Figure C-6  | VL_PACKING_444_8 64             |

|-------------|---------------------------------|

| Figure C-7  | VL_PACKING_R444_8 65            |

| Figure C-8  | VL_PACKING_4444_8 66            |

| Figure C-9  | VL_PACKING_R4444_8 67           |

| Figure C-10 | VL_PACKING_R0444_8 68           |

| Figure C-11 | VL_PACKING_0444_8 69            |

| Figure C-12 | VL_PACKING_4444_10_10_10_2 70   |

| Figure C-13 | VL_PACKING_R4444_10_10_10_2 70  |

| Figure C-14 | VL_PACKING_2424_10_10_10_2Z 71  |

| Figure C-15 | VL_PACKING_R2424_10_10_10_2Z 71 |

| Figure C-16 | VL_PACKING_242_10_in_16_L 72    |

| Figure C-17 | VL_PACKING_242_10_in_16_R 72    |

| Figure C-18 | VL_PACKING_R242_10_in_16_L 73   |

| Figure C-19 | VL_PACKING_R242_10_in_16_R 73   |

| Figure C-20 | 4:4:4 Sampling 74               |

| Figure C-21 | 4:2:2 Sampling 75               |

|             |                                 |

# List of Tables

- Table 1-150-Pin Cable Connectors6

- Table 2-1HD I/O Node Controls16

- **Table 2-2**Controls for the HD I/O Option17

- Table 2-3Values for VL\_TIMING19

- Table 2-4Genlock Sync Source and Timing20

- Table 2-5

VL\_FORMAT and VL\_COLORSPACE Combinations Supported

23

- Table 2-6Color-Space Values24

- Table 2-7HD I/O Events32

- Table A-1Panasonic 50-Pin Connector Pinout (HD-D5)41

- Table A-2Philips 50-Pin Connector Pinout (Spirit DataCine)42

- Table A-3LINK A and LINK B Usage in 4:2:2:4 Mode42

- Table A-4LINK A and LINK B Usage in RGBA Mode43

- **Table A-5**LINK A and LINK B Usage in 4:4:4:4 Mode43

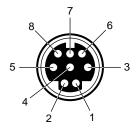

- Table A-6GPI Pinouts45

- Table A-7

GPI Transmitter Electrical Specifications

46

- Table A-8

GPI Receiver Input Optoisolator Electrical Specifications

48

- Table C-1HD I/O Packings61

# About This Guide

The SGI HD I/O option board allows the Silicon Graphics Onyx2 supercomputing workstation to generate and receive uncompressed high-definition television (HDTV) signals in real time. The board is also supported in SGI Origin 2000 servers.

**Note:** This option board requires IRIX 6.5.4 or later; earlier versions of IRIX do not recognize the board.

Features of this option are controlled with the Video Library (VL). VL device-independent calls and controls are explained in the *Digital Media Programming Guide* (007-1799-060 or later; online only).

#### Audience

This guide was written for the sophisticated video user in a professional or research environment. You should be familiar with video standards, the operation of the Silicon Graphics workstation or server, and the VL information in the *Digital Media Programming Guide*.

### **Structure of This Guide**

This guide includes the following chapters and appendices:

- Chapter 1, "Features and Capabilities," outlines the main components of the HD I/O option.

- Chapter 2, "Programming the HD I/O Option," describes using the VL to accomplish common specific tasks.

- Chapter 3, "Synchronizing Data Streams and Signals," explains how to use unadjusted system time (UST) and media stream count (MSC) for the HD I/O board.

- Appendix A, "HD I/O Option Board Specifications," summarizes technical specifications for the option board.

- Appendix B, "Setting Up the HD I/O Board for Your Video Hardware," describes connecting video equipment to HD I/O board connectors and using the control panel *vcp* to configure the board for the equipment.

- Appendix C, "Pixel Packings and Color Spaces," sets forth all packing formats used by the HD I/O hardware.

- Appendix D, "Programming Methods for Real-Time Digital Media Recording and Playback," explains programming concepts, such as real-time disk I/O, and gives examples.

- Appendix E, "Installing HD I/O Software on a New Disk," gives the steps for installing the software, should that become necessary in the case of a new disk.

An index completes this guide.

#### Other Documents

Besides this guide, *Digital Media Connections* (007-3525-003 or later) is shipped with the HD I/O option board. The *Digital Media Programming Guide* (007-1799-060) is available with the IRIX digital media development environment software (*dmedia\_dev*); the online version of this manual is included with IRIS 6.5.4 and later.

It is also a good idea to have your system owner's guide available. If you do not have these guides handy, the information is also online in the following locations:

- IRIS InSight Library: from the Toolchest, choose Help > Online Books > SGI EndUser or SGI Admin, and select the applicable guide.

- Technical Publications Library: if you have access to the Internet, enter the following URL in your Web browser location window: http://techpubs.sgi.com/library/

Once you are in the library, choose Catalogs > Hardware Catalog > and look under the Owner's Guides for the applicable owner's guide. For software guides, look on the bookshelf for the applicable IRIX version.

#### **Conventions Used in This Guide**

In command syntax descriptions and examples, square brackets ([]) surrounding an argument indicate an optional argument. Variable parameters are in *italics*. Replace these variables with the appropriate string or value.

In text descriptions, IRIX filenames are in *italics*.

**Helvetica Bold** font is used for labels on hardware, such as for ports and LEDs on the I/O panel.

Messages and prompts that appear on-screen are shown in typewriter font. Entries that are to be typed exactly as shown are in **boldface typewriter font**.

In each chapter or appendix in which the *Digital Media Programming Guide* is referenced, it is referred to by its full title at the first occurrence and thereafter as the DMPG.

Chapter 1

# Features and Capabilities

The Silicon Graphics HD I/O option board is an XIO card for the Silicon Graphics Onyx2 supercomputing workstation for interfacing to American Television Standards Committee high-definition television video formats, so that it can generate and receive uncompressed HDTV signals in real time.

This chapter consists of the following sections:

- "HD I/O Features" on page 1

- "HD I/O Panel and Cable" on page 5

#### HD I/O Features

Features include the following:

- "Supported Video Formats" on page 1

- "Genlock and Timing Features" on page 2

- "Other Features" on page 2

#### Supported Video Formats

The HD I/O board supports all video formats defined by the Advanced Television Standards Committee (ATSC) that have a pixel clock of up to 74.25 MHz:

- 16 x 9 aspect ratio with 1920, 1280 and 720 active pixels in line, depending on video format

- Support for 24/1.001, 24, 25, 30/1.001, 50, and 60/1.001 Hz vertical rates

Examples of supported formats are SMPTE 274M (interlaced), SMPTE 296 (progressive), SMPTE 295M (interlaced), SMPTE 260M, and SMPTE 293M.

HD I/O formats supported for this release are as follows:

- 1920x1080i@59.94Hz 4:2:2 (8,10-bit)

- 1280x720p@59.94Hz 4:2:2 (8,10-bit)

Both formats are used for content creation and telecine output, and support serial-parallel conversion. Subsequent releases will support additional formats.

#### **Genlock and Timing Features**

Genlock and timing features are all designed to SMPTE 274M timing specifications:

- Genlock to external analog and internal digital sync reference inputs:

- Trilevel analog sync at high-definition (HD) rates

- Bilevel analog sync at standard-definition (SD) rates (with and without output format timing conversion of SD to HD rates)

- Genlock to digital input: locking digital output to jitter-attenuated digital input clock

- Standalone free-run timing:

Uncalibrated free-run mode provides 25 ppm-accurate free-run frequency. After calibration, free-run mode provides higher than 10 ppm-accurate free-run frequency, which can be recalibrated for local references and conditions to as high as 1 ppm accuracy. For information on calibration, see the HD I/O release notes.

#### **Other Features**

Other salient features of the HD I/O option board are:

- Bit-parallel ECL differential interface (special connectors, cable, adapters)

- Automatic adjustment of input phase between Link A and Link B (up to eight input clocks)

- YCrCb 10 or 8 bits per component (4:2:2 or 4:4:4 sampling rates)

- Alpha channel support: 10 or 8 bits (full sampling rate; special connector/cable required)

- Video interface support for RGB 10 or 8 bits (special connector/cable required)

- Support for up to 13 bits RGB in memory

- Real-time transparent color-space conversion and key scaling

- User-programmable horizontal and vertical phase adjustment of the output video

- UST support on input and output

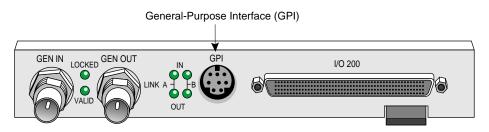

- General-Purpose Interface (GPI) connector, two channels in and two channels out

- Gamma correction support through 13-bit-wide lookup tables

- Board internal loopback mode

Figure 1-1 shows the board.

Figure 1-1 HD I/O Option Board

Figure 1-2 is a simplified top-level diagram of HD I/O option board.

Figure 1-2 HD I/O Board Diagram, Simplified

4

### HD I/O Panel and Cable

Figure 1-3 shows connectors on the HD I/O front panel.

LEDs for Link A and Link B in and out

Figure 1-3 HD I/O Board Connectors

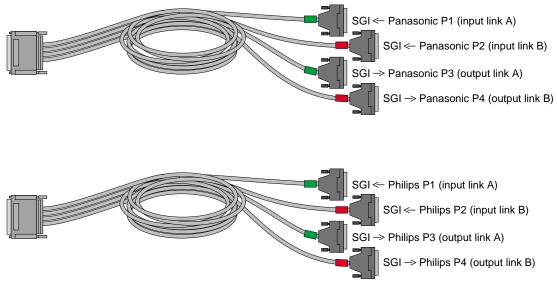

Figure 1-3 shows the two multiheaded cables included with the board; each has four 50-pin connectors for link A input, link B input, link A output, and link B output. The 50-pin connectors differ for each type of cable, following the Panasonic and Philips 50-pin video equipment interface standard.

The cable 50-pin connectors are used as indicated in Table 1-1.

| Table 1-1   | 50-Pin Cable Connectors |                      |               |

|-------------|-------------------------|----------------------|---------------|

| Label Color | Label: Panasonic Cable  | Label: Philips Cable | Use           |

| Green       | SGI < PANASONIC P1      | SGI < PHILIPS P1     | Input Link A  |

| Red         | SGI < PANASONIC P2      | SGI < PHILIPS P2     | Input Link B  |

| Green       | SGI> PANASONIC P3       | SGI> PHILIPS P3      | Output Link A |

| Red         | SGI> PANASONIC P4       | SGI> PHILIPS P4      | Output Link B |

For pinouts, see "Cable Connectors" on page 40 in Appendix A.

The four 50-pin connectors can be used for 4:4:4:4 or 4:2:2:4 in dual-link mode, or 4:2:2 in single-link mode where alpha is ignored:

- In 4:4:4:4 mode, Link A carries Y plus Cr and Cb from even-numbered sample points; Link B carries alpha plus Cr and Cb from odd-numbered sample points.

- In 4:2:2:4 mode, Link A carries Y plus Cr and Cb; Link B carries alpha only.

- In RGBA mode, Link A carries B and G; Link B carries R and alpha.

The video format selected determines Link A and Link B usage. For more information, see the following standards, which contain provisions for video signals:

• SMPTE 240M

SMPTE 240M corresponds to the early 1035i HDTV format; it is being replaced by SMPTE 274M. The HD I/O option supports this model for compatibility with some equipment still using this standard. (This standard also defines color spaces, which must be set with a control, as explained in "VL\_COLORSPACE" on page 22 in Chapter 2.)

- SMPTE 274M (subset, up to 74.25 MHz)

- SMPTE 296M (progressive)

- Recommendation 709 (ITU-R BT.709-2), which defines color primaries used by SMPTE 274M

*Chapter 2*

# Programming the HD I/O Option

The HD I/O option board supports the Video Library (VL). This API is described in the *Digital Media Programming Guide* (007-1799-060 or later; hereafter referred to as the DMPG).

This chapter consists of these sections:

- "VL Basics for the HD I/O Option Board" on page 7

- "HD I/O Controls" on page 14

- "Field Dominance" on page 29

- "HD I/O Events" on page 31

- "Capturing Graphics to Video" on page 31

- "Reporting" on page 32

- "Examples" on page 32

#### VL Basics for the HD I/O Option Board

To build programs that run under VL, you must

- install the *dmedia\_dev* and *dmedia\_eoe* options

- link with *libvl*

- include *dmedia/vl.h* and *dmedia/vl\_xthd.h* for device-dependent functionality

The client library for VL is */usr/lib32/libvl.so*. The header files for the VL are in */usr/include/dmedia*; the main file is *vl.h*. This file contains the main definition of the VL API and controls that are common across all hardware. Several useful digital media programming examples are in */usr/share/src/dmedia/video/XTHD*.

**Note:** When building a VL-based program, you must add *-lvl* to the linking command.

For more information on the Video Library and the API usage, see the latest version of the DMPG.

This section explains

- "VL Concepts" on page 8

- "VL Syntax Elements" on page 9

- "VL Object Classes" on page 9

- "VL Nodes for the HD I/O Option" on page 10

- "VL Data Transfer Functions" on page 12

- "HD I/O Data Flow" on page 13

#### **VL Concepts**

The Video Library defines a basic set of primitives and mechanisms to specify interconnections and controls to achieve the desired setup. The two central concepts for VL are

- *path*: an abstraction for a way of moving data around

- *node*: an endpoint of the path

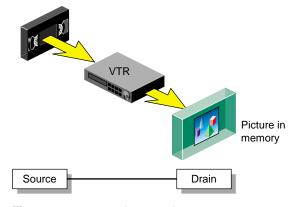

The basic nodes are a *source* (such as a VTR) and a *drain* (such as memory). Figure 2-1 diagrams the simplest VL path, with one of each of these two nodes.

Figure 2-1 Simple VL Path

The HD I/O board has a video source node (the video input), a video drain node (the video output), a memory source node (for output from application), and a memory drain node (for input to application). For transfers, each path must contain exactly one video node and one memory node. HD I/O nodes are further discussed in "VL Nodes for the HD I/O Option" on page 10.

#### **VL Syntax Elements**

VL syntax elements are as follows:

- VL types and constants begin with uppercase VL; for example, VLServer

- VL functions begin with lowercase vl; for example, vlOpenVideo()

#### VL Object Classes

The VL recognizes these classes of objects:

- *devices*, each including sets of nodes

- *nodes*, which are sources, drains, and internal nodes (as discussed in the preceding section)

- *paths*, connecting sources and drains (as discussed in the preceding section)

- *buffers*, for sending and receiving field/frame data to and from host memory

The HD I/O option requires the use of DMbuffers (digital media buffers). DMbuffers, an abstraction of main memory, allow efficient and API-independent interchange of data between the different digital media libraries. For example, video fields can be captured into DMbuffers via VL and then displayed in graphics using OpenGL. They can also be passed between two processes without the data having to be copied explicitly. Refer to Chapter 5, "Digital Media Buffers," in the DMPG for details.

- events, for monitoring video I/O status

- *controls*, or parameters that modify how data flows through nodes; for example:

- video device parameters, such as sync source

- video data parameters such as packing, size, and color space

VL controls fall into two categories:

*device-global* or *device-independent* (prefix VL\_), which can be used by several Silicon Graphics video products

For details of the device-independent controls, refer to the DMPG.

• *device-dependent* (prefix VL\_XTHD\_), specific to a particular video device, in this case, the HD I/O option

Both types of VL controls are explained in this chapter with respect to their usage with The HD I/O option.

#### VL Nodes for the HD I/O Option

Use **vlGetNode()** to specify nodes. This call returns the node's handle, which is used when setting controls or setting up paths. Its function prototype is:

VLNode vlGetNode(VLServer svr, int type, int kind, int number)

In this prototype, variables are as follows:

| svr    | Names the server (as returned by <b>vlOpenVideo()</b> ).                                                                                 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| type   | Specifies the type of node:                                                                                                              |

|        | <ul> <li>VL_SRC: source, such as a digital tapedeck connected to an input port</li> </ul>                                                |

|        | <b>Note:</b> The HD I/O option has only one input.                                                                                       |

|        | • VL_DRN: drain, such as system memory                                                                                                   |

|        | <ul> <li>VL_DEVICE: global control, such as a default source; Table 2-1<br/>summarizes the values for this type</li> </ul>               |

|        | <b>Note:</b> If you are using VL_DEVICE, the <i>VLNode</i> should be set to 0.                                                           |

| kind   | Specifies the kind of node:                                                                                                              |

|        | • VL_VIDEO: connection to a video device equipment; for example, a video tapedeck or camera                                              |

|        | VL_MEM: workstation memory                                                                                                               |

| number | Number of the node in cases of two or more identical nodes, such as two video source nodes. The default value for all <i>kinds</i> is 0. |

VL\_ANY can also be used as a value for *number* to reference the first available node of the specificated *type* and *kind*.

In general, a path for the HD I/O option has a memory node and a video node. The following fragment creates a digital video input source node and a memory drain node, and creates the path:

After nodes are specified, use vlSetControl() to specify parameters:

- memory nodes: you must set packing, color space, size, and capture type

- video nodes: if desired, set video timing, format (for example digital component), and color space; otherwise, the default values displayed in the video control panel (*vcp*) are applied

Controls for each node are defined in "HD I/O Controls" on page 14 in this chapter, and are summarized in Table 2-2. You can set controls in any order.

#### **VL Data Transfer Functions**

This section summarizes VL data transfer categories, and gives the basic steps of creating an application. For the HD I/O option, VL data transfers always involve memory (video to memory, memory to video) and require setting up a DMbuffer pool.

In the VL programming model, the process of creating a VL application consists of these steps:

- 1. Open a connection to the video daemon (vlOpenVideo()).

- 2. Specify nodes on the data path (vlGetNode()).

- 3. Create the path (vlCreatePath()).

- 4. Optional step: add more nodes to a path (vlAddNode()).

- 5. Set up the hardware for the path (vlSetupPaths()).

- 6. Specify path-related events to be captured (vlSelectEvents(), vlAddCallback()).

- Set input and output parameters (controls) for the nodes on the path (vlSetControl()). Video format and timing set in the *vcp* are persistent and default to reasonable values.

- 8. Create a dmBuffer pool to hold data for memory transfers (vlDMGetParams(), dmBufferSetPoolDefaults(), dmBufferCreatePool(), vlGetTransferSize()).

- 9. Register the buffer (vlDMPoolRegister(),vlDMPoolDeregister()).

- 10. Start the data transfer (vlBeginTransfer()).

- Get the data (vlDMBufferGetValid(), vlDMBufferPutValid(), dmBufferAllocate(), dmBufferAllocateSize(), dmBufferGetPoolState(), dmBufferGetPoolFD(), dmBufferSetPoolSelectSize(), dmBufferMapData(), dmBufferFree()) to manipulate frame data.

- 12. Handle data stream events (vlSelectEvents(), vlNextEvent(), vlPending()).

- 13. Clean up (vlEndTransfer(), vlDMPoolDeregister(), vlDestroyPath(), vlCloseVideo()).

Note: Error handling (vlPerror()) is accomplished throughout.

### HD I/O Data Flow

Figure 2-2 diagrams data flow for input.

Figure 2-2 diagrams data flow for output.

Figure 2-3 Data Flow, Output

Figure 2-4 diagrams control flow.

### **HD I/O Controls**

This section consists of the following:

- "Setting Controls" on page 15

- "HD I/O Control Summary" on page 16

- "VL\_TIMING" on page 19

- "VL\_FORMAT" on page 20

- "VL\_PACKING" on page 21

- "VL\_COLORSPACE" on page 22

- "VL\_CAP\_TYPE" on page 27

- "VL\_SIZE and VL\_OFFSET" on page 28

- "VL\_ZOOM" on page 28

#### Setting Controls

After setting up a path, and before starting a transfer, the memory and video nodes must be configured appropriately. Controls on the video node are persistent; that is, they retain their values between path destruction and creation. Memory node controls, however, are reset at each path creation. Because the video node controls are persistent, they need not be set by the application that can deal with arbitrary settings.

For a memory node, the following controls must be set because the default values are likely to be inappropriate:

- VL\_PACKING

- VL\_COLORSPACE

- VL\_CAP\_TYPE

- VL\_SIZE

The recommended way to set VL\_SIZE is to query VL\_SIZE on the video node (after setting VL\_TIMING appropriately) and use the returned value to set VL\_SIZE on the memory node.

On the video node, applications will probably need to set the some controls as well. Most of them can also be set with the video control panel application (*vcp*).

To determine the available devices (that is, video options in the workstation, such as the HDI/O option board) and the nodes available on them, run *vlinfo*. To determine possible controls for each device, enter

vlinfo -l

**Note:** VL controls specified as true with **vlSetControl(**) are executed immediately. However, they are not guaranteed to happen at a specific time.

To set controls for HD I/O nodes, use **vlSetControl()**. The following example sets video format and timing on a node:

```

timing.intVal = VL_TIMING_1125_1920x1080_5994i;

format.intVal = VL_FORMAT_DIGITAL_COMPONENT;

if (vlSetControl(svr, path, drn, VL_TIMING, &timing) <0)

{

vlPerror("VlSetControl:TIMING");

exit(1);

}

```

```

if (vlSetControl(svr, path, drn, VL_FORMAT, &format) <0)

{

vlPerror("VlSetControl:FORMAT");

exit(1);

}</pre>

```

For details on **vlSetControl()** and **vlGetControl()**, see the latest version of the DMPG.

## HD I/O Control Summary

Table 2-1 summarizes node controls for the HD I/O option.

| Control            | Video Source                | Memory Source | Video Drain             | Memory Drain |

|--------------------|-----------------------------|---------------|-------------------------|--------------|

| VL_CAP_TYPE        |                             | Х             |                         | Х            |

| VL_COLORSPACE      | X (YCrCb and<br>RGB_H only) | Х             | X YCrCb and RGB_H only) | Х            |

| VL_FIELD_DOMINANCE | Х                           |               | Х                       |              |

| VL_FORMAT          | Х                           |               | Х                       |              |

| VL_H_PHASE         |                             |               | Х                       |              |

| VL_OFFSET          | X (read only)               | Х             | X (read only)           | Х            |

| VL_PACKING         |                             | Х             |                         | Х            |

| VL_SIZE            | X (read only)               | Х             | X (read only)           | Х            |

| VL_SYNC            |                             |               | Х                       |              |

| VL_SYNC_SOURCE     | Х                           |               | Х                       |              |

| VL_TIMING          | Х                           |               | Х                       |              |

| VL_V_PHASE         |                             |               | Х                       |              |

Table 2-1HD I/O Node Controls

| Table 2-1 (Continued) TID 1/0 Node Controls |              |               |             |              |

|---------------------------------------------|--------------|---------------|-------------|--------------|

| Control                                     | Video Source | Memory Source | Video Drain | Memory Drain |

| VL_XTHD_EE_MODE                             |              | Х             | Х           |              |

| VL_XTHD_INTERFACE_PRECISION                 | Х            |               | Х           |              |

| VL_XTHD_LOOPBACK                            | Х            |               |             |              |

| VL_XTHD_OUTPUT_REPEAT                       | Х            |               |             | Х            |

| VL_ZOOM                                     |              | х             |             | х            |

Table 2-1 (continued)HD I/O Node Controls

**Note:** Except for VL\_XTHD\_VITC\_LINE\_OFFSET, VL\_H\_PHASE, and VL\_\_VPHASE, no controls can be changed during a transfer.

Table 2-2 summarizes the values and uses of controls for the HD I/O option.

| Control            | Values or Range                                                                                                                                                                                                                                                                                                                                        | Use                                                                                                                                                                 |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VL_CAP_TYPE        | VL_CAPTURE_INTERLEAVED<br>VL_CAPTURE_NONINTERLEAVED<br>VL_CAPTURE_FIELDS                                                                                                                                                                                                                                                                               | Selects type of frame(s) or field(s) to<br>capture. See "VL_CAP_TYPE" on page 27<br>in this chapter.                                                                |

| VL_COLORSPACE      | VL_COLORSPACE_REC601_YCRCB<br>VL_COLORSPACE_REC601_YUV<br>VL_COLORSPACE_REC601_RGB_H<br>VL_COLORSPACE_REC601_RGB_F<br>VL_COLORSPACE_240M_YCRCB<br>VL_COLORSPACE_240M_YUV<br>VL_COLORSPACE_240M_RGB_H<br>VL_COLORSPACE_240M_RGB_F<br>VL_COLORSPACE_REC709_YCRCB<br>VL_COLORSPACE_REC709_YUV<br>VL_COLORSPACE_REC709_RGB_H<br>VL_COLORSPACE_REC709_RGB_F | Specifies color space of video data in<br>memory or for input/output. See<br>"VL_COLORSPACE" on page 22 in this<br>chapter.                                         |

| VL_FIELD_DOMINANCE | VL_F1_IS_DOMINANT<br>VL_F2_IS_DOMINANT<br>Note: Frames that are output are deinterlaced<br>differently depending on the choice of output field<br>dominance. Deinterlacing is specified in the<br>application.                                                                                                                                         | Identifies frame boundaries in a field<br>sequence (interlaced formats); ignored by<br>progressive timings.<br>See "Field Dominance" on page 29 in this<br>chapter. |

| Table 2-2 | Controls for the HD I/O Option |

|-----------|--------------------------------|

|-----------|--------------------------------|

| Control                         | Values or Range                                                                                                                                         | Use                                                                                                                                                          |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VL_FORMAT                       | VL_FORMAT_DIGITAL_COMPONENT_DUAL                                                                                                                        | Specifies sampling format of data in or out:<br>Standard YCrCb color space sampled at<br>4:4:4:4 or 4:4:4, depending on packing.                             |

|                                 | VL_FORMAT_DIGITAL_COMPONENT                                                                                                                             | 4:2:2:4 or 4:2:2, depending on packing.<br>See "VL_FORMAT" on page 20 in this<br>chapter.                                                                    |

| VL_H_PHASE                      | [-1000,1000] pixels (increment of 1)                                                                                                                    | Sets horizontal phase.                                                                                                                                       |

| VL_OFFSET                       | Fixed at (0,0).                                                                                                                                         | Sets the position within the video raster to $(0,0)$ .                                                                                                       |

| VL_PACKING                      | See Appendix C, "Pixel Packings and Color Spaces" for values.                                                                                           | Sets packing format for memory source or<br>drain node. See "VL_PACKING" on<br>page 21 in this chapter and Appendix C,<br>"Pixel Packings and Color Spaces." |

| VL_SIZE                         | Raster size.                                                                                                                                            | Memory: Sets size of the desired region of<br>the video raster, which must be the same as<br>the default active region.                                      |

|                                 |                                                                                                                                                         | Video: Returns size of video raster (frame); dependent on timing.                                                                                            |

| VL_SYNC                         | VL_SYNC_INTERNAL<br>VL_SYNC_GENLOCK                                                                                                                     | Sets sync mode for video output.                                                                                                                             |

| VL_SYNC_SOURCE                  | VL_SYNC_HOUSE<br>VL_SYNC_DIGITAL_INPUT_LINK_A<br>VL_SYNC_DIGITAL_INPUT_LINK_B<br>VL_XTHD_SYNC_DIGITAL_INPUT_LINK_A<br>VL_XTHD_SYNC_DIGITAL_INPUT_LINK_B | Selects the genlock source if<br>VL_SYNC_GENLOCK is used.<br>VL_SYNC_HOUSE is analog reference.<br>VL_XTHD_SYNC_DIGITAL_INPUT                                |

| VL_TIMING                       | VL_TIMING_1125_1920x1080_5994i<br>VL_TIMING_750_1280x720_5994p                                                                                          | _LINK_[A   B] on video source node only.<br>Sets or gets timing; see "VL_TIMING" on<br>page 19 in this chapter.                                              |

| VL_V_PHASE                      | [-600,600] lines (increment of 1)                                                                                                                       | Sets vertical phase.                                                                                                                                         |

| VL_XTHD_EE_MODE                 | VL_XTHD_EE_MODE_OFF<br>VL_XTHD_EE_MODE_ON                                                                                                               | Causes digital output to transmit a copy of digital input data; output must be genlocked.                                                                    |

| VL_XTHD_INTERFACE<br>_PRECISION | VL_XTHD_INTERFACE_PRECISION_8<br>VL_XTHD_INTERFACE_PRECISION_10                                                                                         | Specifies whether external video interface is 8 bits or 10 bits wide.                                                                                        |

| <b>Table 2-2 (continued)</b> Controls for the HD I/O Option |                                                                                                        |                                                                                                                                            |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| Control                                                     | Values or Range                                                                                        | Use                                                                                                                                        |  |

| VL_XTHD_LOOPBACK                                            | TRUE<br>FALSE                                                                                          | For video source only, sets video input to<br>the output pipe rather than the input jack<br>(TRUE).                                        |  |

| VL_XTHD_OUTPUT_REPEAT                                       | VL_XTHD_OUTPUT_REPEAT_DISABLED<br>VL_XTHD_OUTPUT_REPEAT_LAST_FIELD<br>VL_XTHD_OUTPUT_REPEAT_LAST_FRAME | Controls whether system repeats<br>DMbuffers output is underflowing; see<br>"Automatically Correcting for Output<br>Underflow" on page 30. |  |

| VL_ZOOM                                                     | 1, -1                                                                                                  | Sets position of top video line in the buffer;<br>see "VL_ZOOM" on page 28 in this<br>chapter.                                             |  |

### **VL\_TIMING**

The VL\_TIMING control sets timing type, which expresses the timing of video presented to a source or drain.

**Note:** For the HD I/O option, VL\_TIMING is specified on the video node only, and not also on the memory mode, as with other Silicon Graphics video options.

Table 2-3 summarizes VL\_TIMING values for the HD I/O option. Future releases will support additional values.

Table 2-3Values for VL\_TIMING

| Timing                         | Sampling Rate (MHz)  | Standard   |

|--------------------------------|----------------------|------------|

| VL_TIMING_1125_1920x1080_5994i | ~74.18 (74.25/1.001) | SMPTE 274M |

| VL_TIMING_750_1280x720_5994p   | ~74.18 (74.25/1.001) | SMPTE 296M |

Each value for VL\_TIMING indicates the raster configuration of a particular SMPTE specification, such as SMPTE 274M-1995 system 3. The values are named according to the raster format:

- The first field is the number of total lines, such as 1125, 750, 525, or 625.

- The second field is the size of the active region, in pixels by lines.

- The third field is the vertical refresh rate and the scanning format; the scanning format is

- i: interlaced

- p: progressive (noninterlaced

For example, VL\_TIMING\_1125\_1920x1080\_5994i specifies 1125 total lines, an active region of 1920 pixels by 1080 lines, 59.94 fields per second, and 2:1interlacing.

**Note:** Although the VL defines timings with sampling rates up through 148.5 MHz, the HD I/O option supports only those through 74.25 MHz.

Timing rates and sync source are interrelated for HDTV. Table 2-4 summarizes the relationships.

| Table 2-4 | Genloc | k Sync | Source | and | Timing | 5 |

|-----------|--------|--------|--------|-----|--------|---|

| Table 2-4 | Genloc | k Sync | Source | and | Timing |   |

| Connector   | Sync Source                        | Output Timing    | Output Timing   | Calibration Timing              | Calibration Timing              |

|-------------|------------------------------------|------------------|-----------------|---------------------------------|---------------------------------|

| GEN IN      | Analog 1920x1080<br>5994i trilevel | 1920x1080 59.94i | 1280x720 59.94p | 1920x1080 59.94i<br>(74.18 MHz) | 1920x1080 59.94i<br>(74.18 MHz) |

|             | Analog NTSC color<br>black bilevel | 1920x1080 59.94i | 1280x720 59.94p | 1920x1080 59.94i<br>(74.18 MHz) | 525<br>(108 MHz)                |

|             | Analog PAL black<br>bilevel        | N/A              | N/A             | 1920x1080 59.94i<br>(74.25 MHz) | 625<br>(108 MHz)                |

| LINK A or B | 1920x1080 59.94i                   | 1920x1080 59.94i | 1280x720 59.94p | N/A                             | N/A                             |

|             | 1280x720 59.94p                    | 1920x1080 59.94i | 1280x720 59.94p | N/A                             | N/A                             |

#### VL\_FORMAT

The VL\_FORMAT control is used on video nodes only. It specifies the sampling format of data on the wire, specifically, dual-link (4:4:4 or 4:4:4:4) or single-link (4:2:2 or 4:2:2:4):

- VL\_FORMAT\_DIGITAL\_COMPONENT\_DUAL: either 4:4:4 or 4:4:4:4, depending on the specified packing

- VL\_FORMAT\_DIGITAL\_COMPONENT: Standard YCrCb color space sampled at 4:2:2 or 4:2:2:4, depending on the specified packing

The memory packing mode VL\_PACKING determines how components are actually sampled.

VL\_FORMAT does not imply color space, nor does it imply whether the second link is used. The second link is used whenever alpha/key channel is used, which depends on the VL\_PACKING setting, or when color is sampled at 4:4:4.

### VL\_PACKING

A video packing describes how a video signal is stored in memory, in contrast to a video format, which describes the characteristics of the video signal. For example, the memory source node accepts packed video from a DMbuffer and outputs video in a given format. Packings are specified through the VL\_PACKING control on the memory nodes.

**Note:** Because of HDTV's multiple color spaces, "old style" packings, such as VL\_PACKING\_Y\_8\_P, are ambiguous and therefore no longer supported for the HD I/O board. You must specify the packing and color space explicitly.

The HD I/O option supports common packings up through 32 bits per pixel, including 4:4:4, 4:2:2, 4:4:4;4, and 4:2:2:4, at 8, 10, and 12 bits per component. Specifically, it supports packings compatible with OpenGL and IRIS GL, and those in common use from other video products. Appendix C, "Pixel Packings and Color Spaces," shows the layout of each packing for the HD I/O option. It also gives the corresponding names for these packings that are used by other libraries.

An application must set both VL\_PACKING and VL\_COLORSPACE. Note that changes in one parameter may change the values of other parameters set earlier; for example, clipped size may change if VL\_PACKING is set after VL\_SIZE. For example:

```

VLControlValue val;

```

```

val.intVal = VL_PACKING_444_8;

vlSetControl(vlSvr, path, memdrn, VL_PACKING, &val);

```

**Note:** Changing this control at the beginning of data transfer takes several seconds to go into effect.

## VL\_COLORSPACE

The VL\_COLORSPACE control specifies color space of video data in memory or for input and output. A color space is a color component encoding format, for example, RGB and YUV. Because video equipment uses more than one color space, the HD I/O video nodes, in addition to the memory nodes, support the VL\_COLORSPACE control.

Each component of an image has

- a color that it represents

- a canonical minimum value

- a canonical maximum value

Normally, a component stays within the minimum and maximum values. For example, for a luma signal such as Y, you can think of these limits as the black level and the peak white level, respectively. For an unsigned component with *n* bits, there are two possibilities for [minimum value, maximum value]:

- full range: [0, (2<sup>nbits</sup>)-1], which provides the maximum resolution for each component

- compressed (headroom) range, which provides numerical headroom, which is often useful when processing video images:

- Cr and Cb:  $[(2^n)/16, 15^*(2^n)/16]$

- Y, A, R, G, and B:  $[(2^n)/16, 235^*(2^n)/256]$

### **Color Spaces and Color Models**

Various HDTV specifications define color models differently from those defined in ITU-R BT.601, which is used by most standard-definition digital video equipment. For HDTV, the VL defines three color models:

- SMPTE 240M

- SMPTE 274M (Recommendation 709, which is ITU-R BT.709-2)

- Recommendation 601

Within each color model, four different color spaces exist:

YCrCb: headroom range

Headroom range means that black is at, for example, code 64 rather than 0, and white is at, for example, code 940 rather than 1023. Headroom-range color spaces can accommodate overshoot (superwhite) and undershoot (superblack) colors. Full-range color spaces clamp these out-of-range colors to black and white.

- YUV: full range

- RGB\_H: headroom range

- RGB\_F: full range

For memory nodes, these four color spaces are defined for each of three color models, resulting in 12 color spaces. Note that all 12 are supported on memory nodes, but only YCrCb and RGB\_H color spaces are supported on video nodes.

Table 2-5 summarizes currently supported combinations of VL\_FORMAT and VL\_COLORSPACE; future releases will support more combinations.

| Table 2-5   | VL_FORMAT and VL_COLC | RSPACE Combinatio |

|-------------|-----------------------|-------------------|

| Video Node  | Memory Node           | -                 |

| 4:2:2 YCrCb | 4:4:4 RGB_F           | -                 |

| 4:2:2 YCrCb | 4:2:2 YCrCb           |                   |

Table 2-5

VL\_FORMAT and VL\_COLORSPACE Combinations Supported

Color-space conversion is performed within a color model if the color spaces are different on the memory and video nodes. Conversion between the color models is not supported.

| Table 2-6                  | Color-Space Va | lues   |                                                |

|----------------------------|----------------|--------|------------------------------------------------|

| Value                      | Standard       | Nodes  | Definition                                     |

| VL_COLORSPACE_REC601_YCRCB | ITU-R BT.601   | All    | Same as VL_COLORSPACE_CCIR601                  |

| VL_COLORSPACE_REC601_YUV   | ITU-R BT.601   | Memory | Full-range YUV (same as VL_COLORSPACE_YUV)     |

| VL_COLORSPACE_REC601_RGB_H | ITU-R BT.601   | All    | Headroom-range RGB (VL_COLORSPACE_RP175)       |

| VL_COLORSPACE_REC601_RGB_F | ITU-R BT.601   | Memory | Full-range Rec. 601 RGB (VL_COLORSPACE_RGB)    |

| VL_COLORSPACE_240M_YCRCB   | SMPTE 240M     | All    | SMPTE 240M YCrCb                               |

| VL_COLORSPACE_240M_YUV     | SMPTE 240M     | Memory | Like 240M_YCRCB but full-range (no headroom)   |

| VL_COLORSPACE_240M_RGB_H   | SMPTE 240M     | All    | Headroom-range RGB                             |

| VL_COLORSPACE_240M_RGB_F   | SMPTE 240M     | Memory | Full-range RGB                                 |

| VL_COLORSPACE_REC709_YCRCB | ITU-R BT.709-2 | All    | 60-Hz YCrCb                                    |

| VL_COLORSPACE_REC709_YUV   | ITU-R BT.709-2 | Memory | Like REC709_YCRCB but full-range (no headroom) |

| VL_COLORSPACE_REC709_RGB_H | ITU-R BT.709-2 | All    | Headroom-range RGB                             |

| VL_COLORSPACE_REC709_RGB_F | ITU-R BT.709-2 | Memory | Full-range RGB                                 |

Table 2-3 summarizes VL\_COLORSPACE values for the HD I/O option.

**Note:** Changing this control at the beginning of data transfer takes several seconds to go into effect.

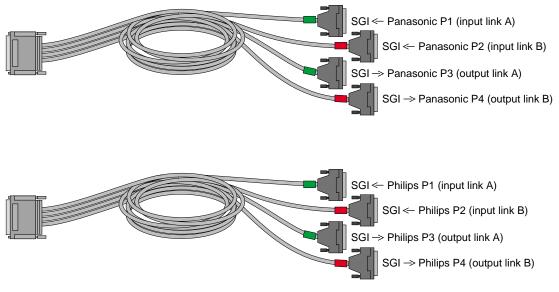

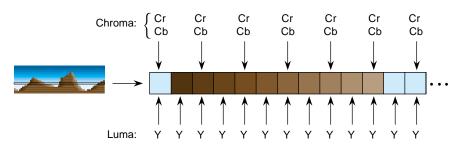

Two sets of colors are commonly used together, RGB (RGBA) and YCrCb/YUV (VYUA). YCrCb (YUV), the most common representation of color from the video world, represents each color by a luma component called Y and two components of chroma, called Cr (or V), and Cb (or U). The luma component is loosely related to brightness or luminance, and the chroma components make up a quantity loosely related to hue. These components are defined rigorously in ITU-R BT.601 (also known as Rec. 601 and CCIR 601), ITU-R BT.709-2, and SMPTE 240M.

The alpha channel is not a real color. For that channel, the canonical minimum value means completely transparent, and the canonical maximum value means completely opaque.

For OpenGL, IRIS GL, and DM:

- the library constant indicates whether the data is RGBA or VYUA

- RGBA data is full-range by default

- VYUA data in DM can be full-range or compressed-range; you must determine this from context

For more information about color spaces, see *A Technical Introduction to Digital Video*, by Charles A. Poynton (New York: Wiley, 1996).

### VL\_COLORSPACE Control of Blanking

Along with memory node color space, VL\_COLORSPACE determines the color-conversion matrix values. In addition, this control affects the type of blanking output by the board during horizontal and vertical blanking, and during active video area when not transferring data. On a video drain node, VL\_COLORSPACE affects the type of blanking that the board outputs, in accordance with SMPTE 274M:

- YCrCb: blanking is Y = 64, Cr/Cb = 512, A = 64

- RGB\_H: blanking is R = 64, G = 64, B = 64, A = 64

### VL\_COLORSPACE and Lookup Tables

The HD I/O board supports lookup tables (LUTs) on input and output for gamma correction or decorrection. If an application is to work with linear components, these can be used to convert between linear and nonlinear spaces.

The HD I/O hardware includes a separate LUT for each RGB color component.Each of the three LUTs is a table of 8192 entries; each entry stores 13 bits. The application programs the entries in each table. LUTs accomplish offsets, if they are required by the memory storage format.

The LUTs perform rounding as follows:

- If the LUT is not explicitly programmed by the application, it is in pass-through mode, and all rounding is performed in the color-space converter.

- If the LUT has been programmed explicitly by the application, the application can control rounding as part of the lookup table function. The packer (hardware that reads the LUT and formats data for the host memory; see Figure 1-2 on page 4) performs a final conversion from 13-bit LUT format to host memory format.

### VL\_COLORSPACE Example

Figure 2-5 summarizes a complicated conversion between color spaces with for 4:2:2 sampling rates and different primary colors. The example shows conversion of material produced using SMPTE 240M colorimetry to material in SMPTE 274M format (ITU-R BT.709.2 colors).

**Note:** In Figure 2-5, RGB are values in linear space and R'G'B' are values in nonlinear space after the optoelectric transfer function is applied as specified in ITU-R BT.709. To convert between RGB and R'G'B', the LUTS can be used to apply this function or its inverse.

# VL\_CAP\_TYPE

An application can request that the HD I/O option capture or play back a video stream in a number of ways. For example, the application can request that each field be placed in its own buffer, or that each buffer contain an interleaved frame. This section explains the capture types that the HD I/O option supports.

Capture types are as follows:

- VL\_CAPTURE\_NONINTERLEAVED

- VL\_CAPTURE\_INTERLEAVED

VL\_CAPTURE\_FIELDS is equivalent to VL\_CAPTURE\_NONINTERLEAVED. The HD I/O option does not support VL\_CAPTURE\_EVEN\_FIELDS and VL\_CAPTURE\_ODD\_FIELDS.

**Note:** VL\_SIZE refers to the size of each frame, rather than the size of the buffer in memory, so it is independent of VL\_CAP\_TYPE; the VL\_CAP\_TYPE setting does not change VL\_SIZE.

#### VL\_CAPTURE\_NONINTERLEAVED

The VL\_CAPTURE\_NONINTERLEAVED capture type specifies that frame-size units are captured noninterleaved. Each field is placed in its own buffer, with the dominant field in the first buffer. If one of the fields of a frame is dropped, all fields are dropped. Consequently, an application is guaranteed that the field order is maintained; no special synchronization is necessary to ensure that fields from different frames are mixed.

If VL\_CAPTURE\_NONINTERLEAVED is specified for playback, similar guarantees apply as for capture. If one field is lost during playback, it is not possible to "take back" the field. The HD I/O option resynchronizes on the next frame boundary, although black or "garbage" video might be present between the erring field and the frame boundary.

### VL\_CAPTURE\_INTERLEAVED

Interleaved capture interleaves the two fields of a frame and places them in a single buffer; the order of the fields depends on the value set for VL\_DOMINANCE\_FIELD.

The HD I/O option guarantees that the interleaved fields are from the same frame: if one field of a frame is dropped, then both are dropped.

During playback, a frame is deinterleaved and output as two consecutive fields, with the dominant field output first. If one of the fields is lost, the HD I/O option resynchronizes to a frame boundary before playing the next frame. During the resynchronization period, black or "garbage" data may be displayed.

### VL\_SIZE and VL\_OFFSET

VL\_SIZE refers to the size of each frame, rather than the size of the buffer in memory, so it is independent of VL\_CAP\_TYPE; the VL\_CAP\_TYPE setting does not change VL\_SIZE.

For memory nodes, VL\_SIZE specifies the desired region of the video raster, which must be the same as the default active region. There is no default; this control must be set. On video nodes, this control is read-only and cannot be set.

For memory nodes, VL\_OFFSET is related to VL\_SIZE; it specifies the origin of the video region to be captured at (0,0), the standard beginning of active video. The recommended way to set VL\_SIZE for the memory node is to query it on the video node (after setting VL\_TIMING appropriately) and use the returned value to set VL\_SIZE on the memory node.

### VL\_ZOOM

The VL\_ZOOM control specifies the site of the top video line in memory; it does not scale (zoom and decimate) a video image as for some other Silicon Graphics video options. The VL\_ZOOM value can be 1 or -1:

- 1: Normal line order; the top video line is at the lowest address in the buffer.

- -1: Inverted line order; as in OpenGL, the top video line is at the highest address in the buffer.

## Field Dominance

Field dominance identifies the frame boundaries in a field sequence; that is, it specifies which pair of fields in a field sequence constitute a frame. The control VL\_FIELD\_DOMINANCE allows you to specify whether an edit occurs on the nominal video field boundary (Field 1, or F1) or on the intervening field boundary (Field 2, or F2).

- F1 dominant: The edit occurs on the nominal video field boundary.

- F2 dominant: The edit occurs on the intervening field boundary.

Whether a field is Field 1 or Field 2 is determined by the setting of bit 9, the F bit, in the XYZ word of the EAV and SAV sequences. The setting means the following:

- For Field 1 (also called the odd field), the F bit is 0.

- For Field 2 (also called the even field), the F bit is 1.

Note: Field dominance has no effect on progressive timings.

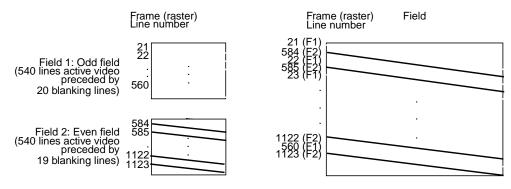

Figure 2-6 shows fields and frames as defined for digital 1080-line formats for the HD I/O option.

Figure 2-6 Fields and Frames for SMPTE 274M

Editing is usually on Field 1 boundaries, where Field 1 is defined as the first field in the video standard's two-field output sequence. However, some users may want to edit on F2 boundaries, which fall on the field in between the video standard's frame boundary. To do so, use this control, then program your deck to select F2 edits.

A set of frames to be output must be deinterlaced into fields differently, depending on the choice of output field dominance: for SMPTE 274M, the top line is in F1, as shown in Figure 2-6; for SMPTE 240M, the top line is in F2. For example, when F1 dominance is selected, the field with the topmost line must be the first field to be transferred; when F2 dominance is selected, the field with the topmost line must be the second field to be transferred.

### Automatically Correcting for Output Underflow

If the application is not sending buffers fast enough for the receiving equipment's video frame rate, you can set VL\_XTHD\_OUTPUT\_REPEAT to repeat DMbuffers automatically. The values for this control vary depending on whether the transfer is progressive or interlaced.

For interlaced noninterleaved transfers, choices are as follows:

VL\_XTHD\_OUTPUT\_REPEAT\_LAST\_FIELD

This setting repeats the last buffer twice. This setting is spacially imperfect, but does not cause flicker.

VL\_XTHD\_OUTPUT\_REPEAT\_LAST\_FRAME (the default)

This setting repeats the last pair of buffers. This setting is spacially better than VL\_XTHD\_OUTPUT\_REPEAT\_LAST\_FIELD, but causes flicker.

• VL\_XTHD\_OUTPUT\_REPEAT\_DISABLED

This setting, which does not resend any data, is the most useful for debugging, since underflow is then quite visible on output.

For progressive or interleaved transfers, choices are as follows:

• VL\_XTHD\_OUTPUT\_REPEAT\_LAST\_FRAME (the default)

This setting repeats the last buffer.

• VL\_XTHD\_OUTPUT\_REPEAT\_DISABLED

## **Capturing Graphics to Video**

To capture graphics to video, you can use OpenGL to read pixels into memory. However, the coordinate system differs between video and Open GL; under OpenGL, the origin is at the lower left corner and in video, origin is in the upper left corner. To adjust for this difference, set VL\_ZOOM to -1; see "VL\_ZOOM" on page 28.

# HD I/O Events

The VL provides several ways of handling data stream events, such as completion or failure of data transfer, vertical retrace event, loss of the path to another client, lack of detectable sync, or dropped fields or frames. The method you use depends on the kind of application you are writing:

- For a strictly VL application, use

- vlSelectEvents() to choose the events to which you want the application to respond

- vlCallback() to specify the function called when the event occurs

- your own event loop or a main loop (vlMainLoop()) to dispatch the events

- For an application that also accesses another program or device driver, or if you are adding video capability to an existing X or OpenGL application, set up an event loop in the main part of the application and use the IRIX file descriptor (FD) of the event(s) you want to add.

For more information on these functions, see Chapter 4 in the DMPG.

Table 2-7 summarizes events for the HD I/O option. For these options, this table supersedes the table of events in Chapter 14, "VL Event Handling," in the DMPG; the HD I/O option supports only the events listed in Table 2-7.

| Event              | Use                                                   |

|--------------------|-------------------------------------------------------|

| VLSyncLost         | Sync is not detected                                  |

| VLStreamStarted    | Stream started delivery                               |

| VLStreamStopped    | Stream stopped delivery                               |

| VLSequenceLost     | A field/frame was dropped                             |

| VLControlChanged   | A control on the path has changed                     |

| VLTransferComplete | A field/frame transfer has completed                  |

| VLTransferFailed   | A transfer has failed and DMA is aborted              |

| VLTransferError    | A transfer error was discovered; field may be invalid |

Table 2-7HD I/O Events

### Reporting

The DMediaInfo structure reports the Unadjusted System Time (UST).

The HD I/O option makes use of the error events noted in Chapter 4 of the DMPG, as well as VLTransferErrorEvent, which reports nonfatal video transfer errors. The VLTransferComplete and VLSequenceLost events also report the Media Stream Count (MSC) of the field or frame transferred or failed.

### Examples

This section contains three examples:

- "Capture to Memory for Disk Recording" on page 33

- "Playback From Memory for Disk Playback" on page 33

- "Capture to Memory for Graphics" on page 34

### Capture to Memory for Disk Recording

This example shows an application that simply captures video data and records it to disk, for later playout. The video is left in its original 4:2:2 sampling and color space. Because 10 bits are required, the R242\_10 packing mode is chosen. Frames start on F1 boundaries. After creating the VL path, the application sets up the video node, mostly as a result of user input, since it depends on external equipment. videoSource.VL\_TIMING = VL\_TIMING\_1125\_1920x1080\_5994i videoSource.VL\_COLORSPACE = VL\_COLORSPACE\_REC709\_YCRCB videoSource.VL\_FIELD\_DOMINANCE = VL\_F1\_IS\_DOMINANT videoSource.VL\_FORMAT = VL\_FORMAT\_DIGITAL\_COMPONENT videoSource.VL\_XTHD\_LOOPBACK = VL\_XTHD\_LOOPBACK\_OFF videoSource.VL\_XTHD\_INTERFACE\_PRECISION = VL\_XTHD\_INTERFACE\_PRECISION\_10

Next, application configures memory node:

```

memoryDrain.VL_SIZE = videoSource.VL_SIZE

memoryDrain.VL_COLORSPACE = videoSource.VL_COLORSPACE

memoryDrain.VL_CAP_TYPE = VL_CAPTURE_NONINTERLEAVED

memoryDrain.VL_PACKING = VL_PACKING_R242_10

```

Next, the application calls **vlGetTransferSize()** to get the required buffer size to hold each field. Using that size, it creates and registers a DMS buffer pool and starts the transfer.

### Playback From Memory for Disk Playback

This example shows an application that plays back data captured in the previous example.

The application in the previous example has stored various attributes along with the data, including color space, frame rate, dominance, and size. These attributes, along with some user-specified options, are used to derive the control values. After creating the VL path, the application sets up the video node:

```

videoDrain.VL_TIMING = VL_TIMING_1125_1920x1080_5994i

videoDrain.VL_COLORSPACE = VL_COLORSPACE_REC709_YCRCB

videoDrain.VL_FIELD_DOMINANCE = VL_F1_IS_DOMINANT

videoDrain.VL_FORMAT = VL_FORMAT_DIGITAL_COMPONENT

videoDrain.VL_XTHD_INTERFACE_PRECISION = VL_XTHD_INTERFACE_PRECISION_10

videoDrain.VL_SYNC = VL_SYNC_GENLOCK

videoDrain.VL_SYNC_SOURCE = VL_XTHD_SYNC_HOUSE

```

Next, the application configures the memory node:

```

memorySource.VL_SIZE = videoDrain.VL_SIZE

memorySource.VL_COLORSPACE = videoDrain.VL_COLORSPACE

memorySource.VL_CAP_TYPE = VL_CAPTURE_NONINTERLEAVED

memorySource.VL_PACKING = VL_PACKING_R242_10

```

Next, the application calls **vlGetTransferSize()** to get the required buffer size to hold each field. Using that size, it creates a DMS buffer pool, allocates, fills, and prequeues some buffers, and starts the transfer.

### **Capture to Memory for Graphics**

In this example, the application captures video and draws it on the graphics screen using OpenGL. This example resembles the *videoin* application.

The incoming video is converted to 10-bit 4:4:4 full-range RGB in an OpenGL-compatible packing format. The 4444\_10\_10\_10\_2 packing is chosen; it is compatible with OpenGL using packed-pixel extension GL\_UNSIGNED\_INT\_10\_10\_2\_EXT pixel format. Video is interleaved in memory into frames, and is written upside down to be compatible with OpenGL's default coordinate system (glPixelZoom of (1.0, 1.0)).

First, video node is configured: videoSource.VL\_TIMING = VL\_TIMING\_1125\_1920x1080\_5994i videoSource.VL\_COLORSPACE = VL\_COLORSPACE\_REC709\_YCRCB videoSource.VL\_FIELD\_DOMINANCE = VL\_F1\_IS\_DOMINANT videoSource.VL\_FORMAT = VL\_FORMAT\_DIGITAL\_COMPONENT videoSource.VL\_XTHD\_LOOPBACK = VL\_XTHD\_LOOPBACK\_OFF videoSource.VL\_XTHD\_INTERFACE\_PRECISION = VL\_XTHD\_INTERFACE\_PRECISION\_10

Next, application configures memory node: memoryDrain.VL\_SIZE = videoSource.VL\_SIZE memoryDrain.VL\_COLORSPACE = VL\_COLORSPACE\_REC709\_RGB\_F memoryDrain.VL\_CAP\_TYPE = VL\_CAPTURE\_INTERLEAVED memoryDrain.VL\_PACKING = VL\_PACKING\_4444\_10\_10\_2 memoryDrain.VL\_ZOOM = -1/1

Next, the application calls **vlGetTransferSize()** to get the required buffer size to hold each field. Using that size, it creates and registers a DMS buffer pool and starts the transfer.

*Chapter 3*

# Synchronizing Data Streams and Signals

You can use special signals recognized or generated by the HD I/O board—UST (unadjusted system time), MSC (media stream count)—to synchronize data streams. This chapter explains

- "Using UST, MSC, and Buffered Media Streams for Synchronization" on page 35

- "Media Library Interfaces for UST and MSC" on page 38

### Using UST, MSC, and Buffered Media Streams for Synchronization

Whenever a VL path is open in continuous mode, the HD I/O board and certain other Silicon Graphics video devices continuously try to dequeue media stream samples from the path's buffer for input, or to enqueue media stream samples onto the path's buffer for output. If the buffer between the application and each device never underflows or overflows, then the application can measure and schedule the timing of input and output signals to 100% of the accuracy of the underlying device.

Occasionally, the application is held off and audio, video, or both come out late. Buffer underflow on output and overflow on input can result from the application not keeping the buffer adequately filled for the following reasons:

- The application is busy with other tasks, allowing too much time between putting fields into the buffer.

- Processes are subject to various interruptions (10 to 80 ms for some processes) under IRIX because

- the process for filling the buffer is running at too low a priority

- the process cannot get a resource from IRIX that it needs, such as memory pages

To get around this problem, a mechanism built into the VL helps keep track of data flow into and out of buffers by providing accurate timing information for each frame of video that enters or leaves the system. This mechanism, called UST/MSC, produces matched pairs of two numbers:

- unadjusted system time (UST), a time value that is used to state timing measurements to applications

- media stream count (MSC), a count value that identifies a particular media stream sample (a video field or frame)

The device keeps a counter called the device media stream count (device MSC), which increments by one every time the device attempts to enqueue or dequeue a media stream sample, whether or not the enqueue or dequeue attempt is successful. UST/MSC was designed to return timing information in a form that is valid whenever the buffer is not underflowing or overflowing.

The UST/MSC capability and the buffering that goes with it are appropriate for applications and devices such as movie players and digital video editing devices.

UST/MSC affords maximally accurate synchronization when scheduling cannot be guaranteed and some buffering is acceptable. Also, if scheduling becomes reliable at some later point, UST/MSC continues to function the same way with no code changes required; the buffers can be made smaller, and the result is a low-latency application with the same accurate synchronization.

Note that UST/MSC itself

does not add any latency to an application

The buffer adds latency: it increases the time the application would take to respond to some output event by changing its input (and vice versa). This solution to the synchronization problem is useful for applications in which a small latency can be sacrificed for more accuracy.

- does not require that an application trade off latency for accuracy

- does not require that an application use any particular size buffer

- delivers the full accuracy of the underlying hardware's timing support regardless of the scheduling characteristics of the application

- could be useful for graphics and texture even for low-latency applications

For the HD I/O option, UST/MSC pairs are maintained in software and are valid only during a transfer. Make calls to **vlGetUSTMSCPair()** and **vlGetFrontierMSC()** only during a transfer; these calls block until at least one buffer has been successfully transferred. Note the following:

- For interlaced timings, MSC always increments by 1 per field.

- For progressive timings, MSC always increments by 1 per frame.

The code below is a high-level algorithm to maintain synchronization of two buffered media streams that send data from memory to hardware outputs; a corresponding one is necessary for the other direction:

```

create video buffer between me and the audio output;

create audio buffer between me and the video output;

while (1)

sleep until one of the buffers is getting empty;

for (video buffer)

{

use UST/MSC to determine:

"at what time (what UST) will the next video data I enqueue

on the buffer actually go out the jack of the machine?";

}

for (audio buffer)

ł

(exact same thing as above, except for audio)

}

From the predicted video and audio USTs, determine

"what is the synchronization error between the audio and video

streams?"

Enqueue more frames to fill up the audio and video buffer queues.

If there is synchronization error, enqueue new frames to either skip

frames on the stream that is behind or repeat frames on the stream

that is ahead.

}

}

```

The answers to the questions in the pseudocode above are obtained with three VL calls that manipulate UST and MSC and are explained in the next section.

### Media Library Interfaces for UST and MSC