# sgi

Linux<sup>®</sup> Device Driver Programmer's Guide – Porting to SGI<sup>®</sup> Altix<sup>®</sup> Systems

#### **COPYRIGHT**

© 2003, 2004, 2005, 2008, Silicon Graphics, Inc. All rights reserved; provided portions may be copyright in third parties, as indicated elsewhere herein. No permission is granted to copy, distribute, or create derivative works from the contents of this electronic documentation in any manner, in whole or in part, without the prior written permission of Silicon Graphics, Inc.

#### LIMITED RIGHTS LEGEND

The software described in this document is "commercial computer software" provided with restricted rights (except as to included open/free source) as specified in the FAR 52.227-19 and/or the DFAR 227.7202, or successive sections. Use beyond license provisions is a violation of worldwide intellectual property laws, treaties and conventions. This document is provided with limited rights as defined in 52.227-14.

#### TRADEMARKS AND ATTRIBUTIONS

SGI, Altix, the SGI cube, the SGI logo, Silicon Graphics, IRIX, and Origin are registered trademarks and NUMAlink is a trademark of Silicon Graphics, Inc., in the United States and/or other countries worldwide.

Intel and Itanium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. Linux is a registered trademark of Linux Torvalds. Motorola is a registered trademark of Motorola, Inc. All other trademarks mentioned herein are the property of their respective owners.

The information in Appendix A, "Memory Operation Ordering on SGI Altix Systems," was originally authored by Jesse Barnes.

# **New Features in This Guide**

This update provides the following:

- Added information about SGI Altix Architecture Considerations for Linux Device

Drivers for SGI ProPack 4 for Linux Service Pack 2 release (or later), which

supersedes this manual, and Linux Device Drivers, third edition, by Jonathan

Corbet, Alessandro Rubini, and Greg Kroah-Hartman, February 2005 (ISBN:

0-596-00590-3) in Chapter 1, "Introduction" on page 1,

- Corrected pgprot\_noncached() macro code example in "PCI-X Memory Resource Address" on page 67.

007-4520-007 iii

# **Record of Revision**

| Version | Description                                                                                                   |

|---------|---------------------------------------------------------------------------------------------------------------|

| 001     | February 2003<br>Original publication                                                                         |

| 002     | June 2003<br>Updated to support the SGI ProPack v2.2 for Linux release.                                       |

| 003     | August 2003<br>Updated to support the SGI ProPack v2.2.1 for Linux release.                                   |

| 004     | May 2004<br>Updated to support the SGI ProPack v3.0 for Linux release.                                        |

| 005     | January 2005<br>Updated to support the SGI ProPack 3 for Linux Service Pack 3<br>release.                     |

| 006     | July 2005<br>Updated to support the SGI ProPack 3 for Linux Service Pack 6<br>release.                        |

| 007     | October 2008<br>Updated to correct code example in chapter 7 (see <i>New Features in This Guide</i> , above). |

007-4520-007 v

# **Contents**

| About This Guide xvi                                    | i |

|---------------------------------------------------------|---|

| Related Resources                                       | i |

| Developer Program                                       | i |

| Internet Resources                                      | i |

| SGI Altix System Documentation                          | i |

| Standards Documents                                     | i |

| Intel Compiler Documentation xiz                        | K |

| Other Intel Documentation                               | K |

| Additional Reading                                      | K |

| Obtaining Publications                                  | K |

| Reader Comments                                         | i |

| 1 Introduction                                          |   |

|                                                         | 1 |

| Legacy Functionality                                    | 2 |

| Special Architectural Considerations                    | 4 |

| Programmable I/O Write Operations                       | 4 |

| Direct Memory Access                                    | 5 |

| Device Interrupts and Posted DMAs                       | 5 |

| PIO Reads and Posted DMAs                               | 5 |

| Polling Memory for Completion and Posted DMA Data       | 5 |

| Porting a Driver to Altix Systems — A Quick Start Guide | 6 |

| Device Driver Registration and Special Device Nodes     | 6 |

| Itanium 2 Processors and Altix System Addresses         | 7 |

| ·                                                       | 7 |

|                                                         |   |

| 007-4520-007                                            | i |

| Bus Addresses - PCI/PCI-X Buses                    | <br>8  |

|----------------------------------------------------|--------|

| Programmable IO Read/Write Addresses               | <br>8  |

| Device Driver Interrupt Registration - IRQs        | <br>ç  |

| Direct Memory Access Addresses (DMA)               | <br>10 |

| Posted PIO write Calls                             | <br>11 |

| 2. Architecture                                    | <br>13 |

| System Components                                  | <br>13 |

| Compute/Processor Node (SC-brick)                  | <br>16 |

| PCI-X with BaseIO (IX-brick)                       | <br>18 |

| PCI-X with Expansion (PX-brick)                    | <br>19 |

| System Memory Address Space                        | <br>20 |

| Physical Address Space                             | <br>21 |

| Global MMR Space                                   | <br>22 |

| AMO Space                                          | <br>23 |

| Cacheable Memory Space                             | <br>25 |

| Cache Use                                          | <br>25 |

| Cache Coherency                                    | <br>26 |

| SHub Physical Address Map                          | <br>26 |

| PIO Addresses and DMA Addresses                    | <br>27 |

| PIO Addressing                                     | <br>29 |

| PIO Addressing Extension                           | <br>29 |

| DMA Addressing                                     | <br>30 |

| DMA Addressing Extension                           | <br>30 |

| Linux Kernel and User Virtual Address Management . | <br>30 |

| Memory Access                                      | 31     |

| CPU Access to Memory or I/O Address Space          | <br>31 |

viii 007–4520–007

| CPU Access to Memory                                                 | 31              |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| CPU Access to I/O Address Space - Programmable I/O (PIO)             | 33              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Device Access to System Physical Memory Space – Direct Memory Access | 35              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3. PCI-X Device Attachment                                           |                 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                      | <b>37</b><br>37 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                      | 38              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| PCI-X Implementation                                                 | 40              |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                      | 40              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| •                                                                    | 41              |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                      | 42              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| •                                                                    | 42              |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                      | 42              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| **                                                                   | 43              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 6                                                                    | 43              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| ** *                                                                 | 44              |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                      | 44              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 4. PCI System Initialization                                         | 47              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 5. Finding Your PCI Device                                           | 51              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Physical Location of Your PCI Device                                 | 51              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Logical Address of Your PCI Device                                   | 52              |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                                                                      | 53              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| ·                                                                    | 55              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 6. PCI/PCI-X Configuration Space                                     | 57              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 7. PCI-X I/O and Memory Resources                                    | 61              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 007-4520-007                                                         | ix              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Anatomy of a PIO Address                     |   |   |   | 61         |

|----------------------------------------------|---|---|---|------------|

| PIO Addresses                                |   |   |   | 61         |

| Flow of PIO Operation                        |   |   |   | 62         |

| Targeting a PCI-X Device on a Local Node     |   |   |   | 62         |

| Targeting a PCI-X Device on a Remote Node    |   |   |   | 64         |

| PIO Address Translation from CPU to PCI Bus  |   |   |   | 65         |

| PCI-X PIO Resource Management                |   |   |   | 66         |

| PCI-X I/O Resource Address                   |   |   |   | 66         |

| PCI-X Memory Resource Address                |   |   |   | 67         |

| PCI-X I/O Resource Reservation               |   |   |   | 68         |

| PCI-X I/O Resource Use Macros                |   |   |   | 69         |

| PCI-X Memory Resource Use Macros             |   |   |   | 70         |

| PIO Write (Posted) Synchronization           |   |   |   | 70         |

| PIO Read Flushing Posted DMA Buffers         |   |   |   | 73         |

| P. DCI V Interment Machaniam                 |   |   |   | 77         |

| 8. PCI-X Interrupt Mechanism                 | • | • | • | <b>7</b> 5 |

| Interrupt Architecture                       | • | • | • | 75         |

| Interrupt Request (IRQ) Management           | • | • | • | 75         |

| Driver Interrupt Registration                | • | • | • | 75         |

| 9. PCI-X Direct Memory Access (DMA)          |   |   |   | 77         |

| Types of DMA Mappings                        |   |   |   | 79         |

| Consistent DMA Mappings                      |   |   |   | 79         |

| Streaming DMA Mappings                       |   |   |   | 79         |

| Anatomy of a Mapped DMA Address              |   |   |   | 80         |

| Format of 32-bit Direct Mapped DMA Addresses | • | • | • | 80         |

| Format of 32-bit DMA Page Mapped Addresses   | • | • | • | 82         |

|                                              | • | • | • | 83         |

| Format of a 64-bit DMA Mapped Adddress       | • | • | • | ŌĴ         |

x 007–4520–007

χi

| PCI-X DMA Address Management                               |   | 83  |

|------------------------------------------------------------|---|-----|

| PCI-X DMA Mapped Routines                                  |   | 84  |

| 10. Device Driver Memory Usage                             | • | 87  |

| Device Driver Memory Allocation                            |   | 87  |

| Allocating Page Boundary Memory                            |   | 87  |

| Allocating Page Boundary Memory on Specific Nodes          |   | 88  |

| Allocating Byte-Range Memory                               |   | 88  |

| Accessing the User Memory Area                             |   | 88  |

| Disabling Validity Checking                                |   | 90  |

| Directly Mapping User Virtual Addresses                    |   | 90  |

| 11. Time Management                                        |   | 93  |

| Interval Timer Counter (ITC)                               |   | 93  |

| Delaying Execution — Short Delay                           |   | 93  |

| Delaying Execution — Long Delay                            |   | 94  |

| 12. Building Linux Kernels and Modules                     |   | 95  |

| Default Configuration File                                 |   | 95  |

| Building a New Linux Kernel                                |   | 95  |

| Booting Your New Linux Kernel                              |   | 95  |

| Rebuilding Modules                                         |   | 96  |

| Downloading SGI Altix RPMs                                 |   | 97  |

| Building New Modules                                       |   | 98  |

| Appendix A. Memory Operation Ordering on SGI Altix Systems |   | 101 |

| Memory Ordering                                            |   | 101 |

| Release Semantics                                          | • | 101 |

|                                                            | • | 102 |

|                                                            |   |     |

007-4520-007

#### Contents

| Index             |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   | • | • |   |   | 107 |

|-------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| Memory Fencing    | • | • | • | • | • | • | • | • | • |   | • | • | • | ٠ | • |   | • | • | • | 105 |

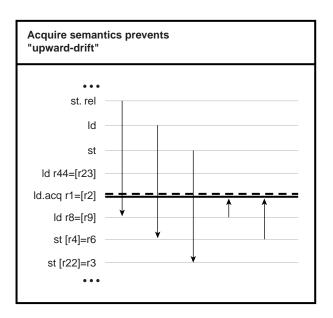

| Acquire Semantics |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 103 |

xii 007–4520–007

# **Figures**

| Figure 2-1  | Links Between Bricks                              | . 15 |

|-------------|---------------------------------------------------|------|

| Figure 2-2  | SC-brick Block Diagram                            | . 17 |

| Figure 2-3  | IX-brick (PX-brick with BaseIO Card)              | . 19 |

| Figure 2-4  | PX-brick - PCI-X Expansion Brick                  | . 20 |

| Figure 2-5  | Address Decoding for Physical Memory Access       | . 21 |

| Figure 2-6  | Bit Values for Global MMR Space                   | . 23 |

| Figure 2-7  | Bit Values for AMO Space                          | . 24 |

| Figure 2-8  | SHub Physical Address Map                         | . 27 |

| Figure 2-9  | Device Access through a Bus Adapter               | . 28 |

| Figure 2-10 | CPU Access to Memory                              | . 32 |

| Figure 2-11 | CPU Access to Device Registers (Programmable I/O) | . 34 |

| Figure 2-12 | Device Access to Memory                           | . 35 |

| Figure 3-1  | PX-brick with BaseIO                              | . 38 |

| Figure 3-2  | PX-brick PCI-X Expansion                          | . 39 |

| Figure 3-3  | PCI-X Implementation                              | . 40 |

| Figure 5-1  | Physical Address Components                       | . 52 |

| Figure 6-1  | PCI-X Configuration Space                         | . 58 |

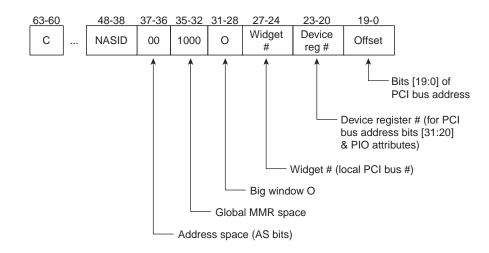

| Figure 7-1  | PIO Address Format                                | . 62 |

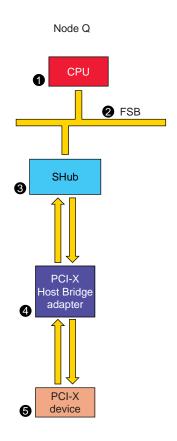

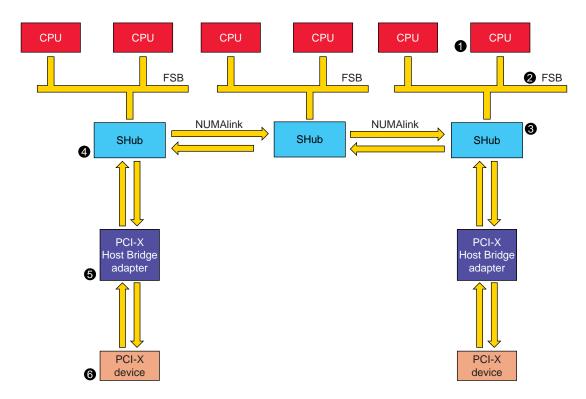

| Figure 7-2  | PIO to a Local PCI-X Device                       | . 63 |

| Figure 7-3  | PIO to a Remote PCI-X Device                      | . 64 |

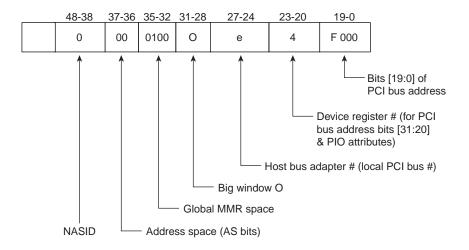

| Figure 7-4  | PIO Address from the CPU                          | . 65 |

| Figure 9-1  | DMA to Memory on A Local Node                     | . 77 |

| Figure 9-2  | DMA to Memory on A Remote Node                    | . 78 |

| 007-4520-00 | 07                                                | xiii |

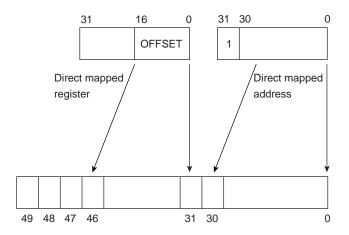

| Figure 9-3 | PCI Direct Mapped Register (one per PCI bridge)        | 81 |

|------------|--------------------------------------------------------|----|

| Figure 9-4 | 32-bit Direct Mapped Address As Returned by the System | 81 |

| Figure 9-5 | 50-bit System Memory Address                           | 81 |

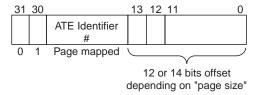

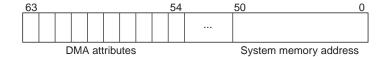

| Figure 9-6 | 32-bit DMA Mapped Address                              | 82 |

| Figure 9-7 | 64-bit DMA Mapped Address                              | 83 |

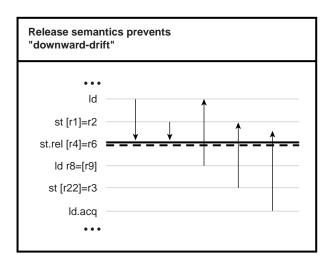

| Figure A-1 | Release Semantics One-Directional Fence                | 03 |

| Figure A-2 | Acquire Semantics One-Directional Fence                | 04 |

| Figure A-3 | Two-dimensional Memory Fence (mf)                      | 05 |

xiv 007–4520–007

# **Tables**

| Table 3-1 | Bandwidth Characteristics of the IX-brick |  |  |  |  |  |  | 37 |

|-----------|-------------------------------------------|--|--|--|--|--|--|----|

| Table 3-2 | Bandwidth Characteristics of the PX-brick |  |  |  |  |  |  | 39 |

| Table 3-3 | Shared Interrupts                         |  |  |  |  |  |  | 4  |

| Table 7-1 | Memory Locks                              |  |  |  |  |  |  | 71 |

| Table 7-2 | Correct Memory Lock Usage                 |  |  |  |  |  |  | 72 |

007–4520–007 xv

# **About This Guide**

This guide describes the ways in which hardware devices are integrated into and controlled from an SGI Altix series system running the Linux operating system. This guide provides an overview of the unique elements of writing drivers for SGI systems, a description of the SGI Altix architecture, and a summary of the SGI Linux kernel resources.

To write a **process-level** driver, you must be an experienced C programmer with a thorough understanding of the use of Linux system services and, of course, detailed knowledge of the device to be managed.

To write a **kernel-level** driver, you must be an experienced C programmer who knows Linux system administration and who understands the concepts of Linux device management.

# **Related Resources**

The resources listed in this section contain additional information that might be helpful.

#### **Developer Program**

Information and support are available through the SGI Developer Program. To join the program, contact the Developer Response Center at 800-770-3033 or e-mail devprogram@sgi.com.

#### **Internet Resources**

A great deal of useful material can be found on the Internet. Some starting points are in the following list.

http://docs.sgi.com

SGI technical manuals to read or download

007–4520–007 xvii

**Note:** Make sure you search in the entire Technical Publications Library (TPL) to view Linux and Altix systems documentation.

http://www.pcisig.com

Home page of the PCI bus standardization organization

#### **SGI Altix System Documentation**

For additional information on SGI Altix system documentation, see the following:

· SGI ProPack for Linux Start Here

Provides a comprehensive list of SGI Altix system hardware and software documentation

• SUSE LINUX for SGI Altix Systems

Provides a comprehensive list of SGI Altix system hardware and software documentation

• http://docs.sgi.com

SGI technical manuals to read or download

**Note:** Make sure you search in the entire Technical Publications Library (TPL) to view Linux and Altix systems documentation.

• SGI Altix Architecture Considerations for Linux Device Drivers

This manual contains information about device drivers specific to SGI Altix systems running an SGI ProPack 4 for Linux Service Pack 2 release (or later).

#### **Standards Documents**

The following documents are the official standard descriptions of buses:

• *PCI Local Bus Specification, Version 2.1*, available from the PCI Special Interest Group, P.O. Box 14070, Portland, OR 97214 (fax: 503-234-6762).

xviii 007–4520–007

• *ANSI/IEEE standard 1014-1987* (VME Bus), available from IEEE Customer Service, 445 Hoes Lane, PO Box 1331, Piscataway, NJ 08855-1331.

#### **Intel Compiler Documentation**

Documentation for the Intel compilers is located on your system in the /docs directory of the directory tree where your compilers are installed. If you have installed the Intel compilers, the following documentation is available:

- Intel C++ Compiler User's Guide (c ug lnx.pdf)

- Intel Fortran Compiler User's Guide (for ug lnx.pdf)

- Intel Fortran Programmer's Reference (for prg.pdf)

- Intel Fortran Libraries Reference (for lib.pdf)

#### Other Intel Documentation

The following documents describe the Itanium (previously called "IA-64") architecture and other topics of interest:

• Intel Itanium 2 Processor Reference Manual for Software Development and Optimization, available online at the following location:

http://developer.intel.com/design/itanium2/manuals/251110.htm

• Intel Itanium Architecture Software Developer's Manual, available online at the following location:

http://developer.intel.com/design/itanium/manuals/iiasdmanual.htm

• Introduction to Itanium Architecture, available online at the following location:

http://shale.intel.com/softwarecollege/CourseDetails.asp?courseID=13

(secure channel required)

007-4520-007 xix

#### **Additional Reading**

The following additional publications are referenced in this manual:

- David Mosberger and Stephane Eranian, IA-64 Linux Kernel Design and Implementation. Prentice Hall, http://www.phptr.com. ISBN 0-13-061014-3.

- Alessandro Rubini and Jonathan Corbet, *Linux Device Drivers*. Second edition, June 2001. O'Reilly, 0–59600–008–1, order number: 0081. Also available at http://www.xml.com/ldd/chapter/book/index.html.

- Tom Shanley, PCI-X System Architecture. First edition, 2001. Mindshare Inc. Addison-Wesley, ISBN 0-2-1-72682-3.

- Tom Shanley and Don Anderson, PCI System Architecture. Third edition. Mindshare Inc.

# **Obtaining Publications**

You can obtain SGI documentation as follows:

- See the SGI Technical Publications Library at http://docs.sgi.com. Various formats

are available. This library contains the most recent and most comprehensive set of

online books, release notes, man pages, and other information.

- If it is installed on your SGI system, you can use InfoSearch, an online tool that

provides a more limited set of online books, release notes, and man pages. With

an IRIX system, enter infosearch at a command line or select Help >

InfoSearch from the Toolchest.

- On IRIX systems, you can view release notes by entering either grelnotes or relnotes at a command line.

- On Linux systems, you can view release notes on your system by accessing the README.txt file for the product. This is usually located in the /usr/share/doc/productname directory, although file locations may vary.

- You can view man pages by typing man title at a command line.

xx 007–4520–007

## **Reader Comments**

If you have comments about the technical accuracy, content, or organization of this publication, contact SGI. Be sure to include the title and document number of the publication with your comments. (Online, the document number is located in the front matter of the publication. In printed publications, the document number is located at the bottom of each page.)

You can contact SGI in any of the following ways:

• Send e-mail to the following address:

techpubs@sgi.com

- Contact your customer service representative and ask that an incident be filed in the SGI incident tracking system.

- Send mail to the following address:

SGI Technical Publications 1140 East Arques Avenue Sunnyvale, CA 94085–4602

SGI values your comments and will respond to them promptly.

007–4520–007 xxi

## Introduction

This document provides a description of issues that affect Linux device drivers executing on SGI Altix series systems. SGI Altix systems use a global-address-space cache-coherent multiprocessor that can scale up to 512 processors in a cache-coherent domain. For more information on system components, see "System Components" on page 13.

**Note:** For SGI ProPack 4 for Linux Service Pack 2 release (or later), see *SGI Altix Architecture Considerations for Linux Device Drivers*, which supersedes this manual.

For SGI ProPack 4 Service Pack 2 release (or later), if you are writing or porting a device driver to an SGI Altix, see *Linux Device Drivers*, third edition, by Jonathan Corbet, Alessandro Rubini, and Greg Kroah-Hartman, February 2005 (ISBN: 0-596-00590-3). It provides detailed information about supporting computer peripherals under the Linux operating system based on the 2.6 kernel. It provides information on how to write drivers for a wide variety of devices. It is available at the following location: http://www.oreilly.com/catalog/linuxdrive3/

This document does not provide a tutorial on how to write a Linux device driver on this or any other Linux platform, but assumes that you can write a Linux device driver. It provides information you need for porting a Linux device driver, rewriting a Linux device driver, or writing a new Linux device driver for this platform. If you have never written a Linux device driver, you should start with *Linux Device Drivers*, second edition. This book provides an excellent background, with many examples, for writing a Linux device driver. Similarly, the book, *IA-64 Linux Kernel Design and Implementation*, provides details on the implementation of IA-64 Linux on the Intel Itanium family of processors, which is the architecture on which the SGI Altix is based. Authors and publishers of these books are listed in the Preface ("About This Guide").

**Caution:** Drivers developed by using the information contained in this guide are the responsibility of the user. SGI does not extend any warranty to devices not officially supported by SGI. For information on devices officially supported on SGI and the support terms associated with them, see your support agreement.

Topics discussed in this document are as follows:

007–4520–007

- Chapter 2, "Architecture" on page 13

- Chapter 3, "PCI-X Device Attachment" on page 37

- Chapter 4, "PCI System Initialization " on page 47

- Chapter 5, "Finding Your PCI Device" on page 51

- Chapter 6, "PCI/PCI-X Configuration Space" on page 57

- Chapter 7, "PCI-X I/O and Memory Resources" on page 61

- Chapter 8, "PCI-X Interrupt Mechanism" on page 75

- Chapter 9, "PCI-X Direct Memory Access (DMA)" on page 77

- Chapter 10, "Device Driver Memory Usage" on page 87

- Chapter 11, "Time Management" on page 93

- Chapter 12, "Building Linux Kernels and Modules" on page 95

- Appendix A, "Memory Operation Ordering on SGI Altix Systems" on page 101

This chapter addresses the following topics:

- "Legacy Functionality" on page 2

- "Special Architectural Considerations" on page 4

- "Porting a Driver to Altix Systems A Quick Start Guide" on page 6

# **Legacy Functionality**

Certain "legacy" methods are available to device drivers on other Linux systems that SGI Altix systems do not support (for example, using legacy I/O port numbers 0 through 64K, reading and using peripheral component interconnect (PCI) configuration base address registers (BARs) or interrupt requests (IRQs) directly from the card's configuration space, and so on). Drivers that use legacy methods are not portable and they will not execute correctly on SGI Altix systems.

The SGI Altix system does not always impose upon a Linux device driver the use of additional or different sets of Linux DKIs to function correctly on this platform. However, the SGI Altix system is a large, complex system, and for drivers to successfully invoke the full parallelism of the hardware and hence achieve optimal

performance, it might well be necessary to invoke services and paradigms that are not available in the standard Linux DKI. For specific information, see your SGI support representative.

SGI Altix systems, which run Linux, provide the same I/O capabilities as the SGI Origin series systems, which run IRIX, except for the Intel processor and the little endian platform. The following list describes the legacy functionalities that are **not** available on the SGI Altix platform.

| Legacy                          | Description                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Functionality I/O ports         | SGI Altix I/O subsystems do not support legacy I/O ports from either the Linux kernel or user level applications. If you use legacy I/O port numbers 0 – 65K in I/O port macros such as inb() and outb(), the system will generate an exception.                                                                                                                                                             |  |  |

| Expansion ROM                   | SGI Altix systems do not read and execute basic input/output systems (BIOS) in expansion read-only memory (ROM), even if the ROM is present. Drivers and cards that depend on initialization by these BIOS might not function correctly on this platform. All initialization must be done by the drivers when the Linux kernel calls them to initialize.                                                     |  |  |

| RAM VGA video<br>memory         | SGI Altix systems do not support legacy video random access memory (RAM).                                                                                                                                                                                                                                                                                                                                    |  |  |

| IRQs in PCI configuration space | SGI Altix systems provide IRQs greater than 256. The device driver cannot use the IRQ byte in the PCI configuration space. Device drivers are required to retrieve the IRQ number initialized by the kernel for that device in the pci_dev structure.                                                                                                                                                        |  |  |

| Base Address Registers          | SGI Altix I/O subsystem PCI bridges cannot generate a "dual address" cycle for programmable I/O addresses on the PCI-X bus. As such, only 32 bits of the BARs can be initialized. However, the platform also requires a PIO address to be 64 bits wide. As such, the values in the BARs are not the same as the addresses that the device driver uses on the CPU. The addresses on the CPU have been mapped. |  |  |

007-4520-007 3

Reading the BAR and using it in any I/O macros will cause an exception. PCI-X I/O and memory addresses for the devices are provided in the pci\_dev structure. These values are already mapped and using them will correctly target the relevent PCI-X device.

Peripheral buses

The only peripheral buses that SGI Altix systems support are PCI-X buses. SGI Altix systems do not support traditional legacy I/O space such as I/O ports. PCI-X I/O resource space and memory resource space are presented to the device driver as uncached virtual addresses. For more details, see Chapter 3, "PCI-X Device Attachment" on page 37.

# **Special Architectural Considerations**

The following sections describe special architectural characteristics of SGI Altix systems.

## **Programmable I/O Write Operations**

Programmable I/O (PIO) write operations on SGI Altix I/O subsystems can be cached in various components of the system, from the CPU to the PCI-X bridges. PIO write requests from the same CPU are guaranteed to be issued in program order. However, they are not synchronous. PIO write operations on this platform are posted. To guarantee that PIO write operations have completed, device drivers are required to push all prior PIO write operations out to the device by issuing a PIO read operation to the same controller after the last write operation before releasing a semaphore. This will prevent another CPU from acquiring the semaphore and having its PIO transactions complete before the previous holder of the semaphore.

PIO access and system memory access use different paths and hardware components on SGI Altix I/O subsystems. A get/release operation on a memory-based lock can complete before a PIO write request.

You are strongly advised to program device drivers to flush all relevent PIO write operations with a PIO read operation to the same controller prior to releasing the relevent memory-based locks.

PIO write operation caching is a performance feature. Making each PIO write operation synchronous incurs unneccessary performance penalty. Other Linux based

platforms also require the device driver to explicitly execute PIO write flushing for correct operation.

## **Direct Memory Access**

SGI Altix I/O subsystems provide support for posted direct memory access (DMA). With posted DMA capability, the host bridge can respond to the requester that the request is complete prior to actually transferring the data to target memory. This is a performance feature. DMA data is not guaranteed to arrive in memory "in-order".

## **Device Interrupts and Posted DMAs**

SGI Altix I/O subsystems use the interrupt mechanism to flush all posted DMA data to target memory. This is the only mechanism currently available to ensure that all posted DMAs are flushed into the target memory.

#### PIO Reads and Posted DMAs

PCI-X bridge chipsets on SGI Altix systems do not automatically flush Posted DMA writes on any PIO reads. For information regarding software flushing of posted DMA write buffers, see "PIO Read Flushing Posted DMA Buffers" on page 73.

#### Polling Memory for Completion and Posted DMA Data

On SGI Altix systems, direct memory access (DMA) data from controller cards to system memory is not guaranteed to arrive "in-order". If a device driver is polling a memory location for completion status and the completion status is the last DMA operation by the controller card, it is not guaranteed that all the prior DMA data will arrive in memory before the DMA completion status word. If you are polling memory for completion status, you must use the equivalent mapping routines for this "Completion Status". The equivalent mapping routine provides a DMA handle to flush all DMA data.

Using the appropriate mapping routine will ensure that all prior DMA data has arrived in memory before the "Completion Status" DMA data.

The Linux operating system provides two separate DMA mapping interfaces:

Consistent mapping

007-4520-007 5

Streaming mapping

For information on these mapping interfaces, see "Types of DMA Mappings" on page 79.

# Porting a Driver to Altix Systems — A Quick Start Guide

This section provides a summary of major items to consider when porting your driver to an SGI Altix system and Itanium 2 processors, as follows:

- "Device Driver Registration and Special Device Nodes" on page 6

- "Itanium 2 Processors and Altix System Addresses" on page 7

- "System Physical Memory Addresses" on page 7

- "Bus Addresses PCI/PCI-X Buses" on page 8

- "Programmable IO Read/Write Addresses" on page 8

- "Device Driver Interrupt Registration IRQs" on page 9

- "Direct Memory Access Addresses (DMA)" on page 10

- "Posted PIO write Calls" on page 11

#### **Device Driver Registration and Special Device Nodes**

If your Altix system has devfs configured and activated, you need to ensure that your calls to these functions:

```

register_chrdev()

unregister_chrdev()

register_blkdev()

unregister_blkdev()

```

can be conditionally compiled to call devfs, as follows:

```

devfs_mk_dir()

devfs_register()

devfs_unregister()

```

#### Itanium 2 Processors and Altix System Addresses

All addresses on an Altix system are 64 bits long . Drivers have to ensure that any structures that are allocated to store any addresses must be 64 bits long.

**Note:** It is very important to note that if you want to translate a virtual memory address into a bus address (DMA for the card), using the following macros for translation **WILL NOT** work:

```

bus_to_virt()

virt to bus()

```

An **Example** such as the following, will **not** work:

```

/* This will NOT work ... */

dmabuf = kmalloc(size, GFP_KERNEL);

writel(virt to bus(dmabuf), card's dma addr reg);

```

For more information, see "Direct Memory Access Addresses (DMA)" on page 10

## **System Physical Memory Addresses**

An SGI Altix system does not have system physical memory smaller than or equal to 32 bits. To the device driver, system physical memory addresses are always 64 bits long.

The following macros will provide proper translation from physical-to-virtual or virtual-to-physical:

```

phys_to_virt()

virt_to_phys()

```

**Note:** A system physical address is not the same as a bus address. Therefore, system physical addresses cannot be used by the card for DMA, as is (see "Bus Addresses - PCI/PCI-X Buses" on page 8).

007–4520–007

#### Bus Addresses - PCI/PCI-X Buses

Bus addresses are addresses that allow the device to perform DMA operations from the card into system physical memory. An SGI Altix system supports either a 64-bit bus address or a 32-bit bus address. These bus addresses must be obtained from the various pci\_map\_xxx() routines. See the section on direct memory access ddresses (DMA). Legacy macros like virt\_to\_bus() and bus\_to\_virt() do **not** provide the correct translation.

**Note:** On an Altix system, there is no way to translate a bus address to virtual address. Moreover, there are no reasons why a driver needs to translate a bus Address to a virtual Address. Drivers are responsible to save the the corresponding virtual address to the mapped DMA address. For more information, see "Direct Memory Access Addresses (DMA)" on page 10.

## **Programmable IO Read/Write Addresses**

The following legacy routines do almost no work on Intel Itanium 2 platforms:

- ioremap() Adds the IA64 uncache OFFset

- iounmap() Does nothing

- ioremap nocache() Calls the ioremap() function

Drivers must use the IO addresses provided in the pci dev structure for the device.

An **Example** such as the following, will **not** work:

```

/* This will not work .. */

pci_read_config_dword(pci_dev, PCI_BASE_ADDRESS_0, &ioaddr);

cards_regs = ioremap(ioaddr, 0x1000);

writel(0x60002,(cards_regs + (PCI_INT_CFG/PltfMsk)));

```

Base address registers in the PCI Configuration Space of a card cannot be used, as is, by the device driver for PIO. Device Drivers have to use addresses initialized in the pci dev structure allocated by the system for that device via this routine, as follows:

```

pci_resource_start(dev,bar)

```

Other resource routines of interest are, as follows:

```

pci_resource_end(dev,bar)

pci_resource_flags(dev,bar)

pci_resource_len(dev,bar)

```

On an SGI Altix system, these addresses are 64 bits long, regardless of whether they are PCI IO or memory resources. PCI IO resource addresses can then be used in the following macros:

```

inb/inw/inl/outb/outw/outl

insb/insw/insl/outsb/outsw/outsl

```

**Note:** Hardcoded legacy addresses for example, IO Port Number 0x360, used in IN/OUT macros will not work, for example, inb(0x360), and so on.

PCI memory resource addresses can then be used in the following macros:

```

readb/readw/readl/readq/writeb/writew/writel/writeq

```

#### **Device Driver Interrupt Registration - IRQs**

Device drivers register their interrupt handling routines by calling the following code:

Of particular interest here is <code>irq</code> integer, which traditionally is the interrupt line in the PCI configuration space. Device drivers should **not** be reading this value from the PCI configuration space to get the <code>irq</code> value for the <code>request\_irq()</code>. Instead, device drivers should use the <code>irq</code> number as allocated in the <code>pci\_dev</code> structure by the Linux operating system, as follows:

```

pci dev->irq

```

An **Example** such as the following, will **not** work:

```

/* This will not work .. */

pci_read_config_byte(pci_dev, PCI_INTERRUPT_LINE, &irq);

request irq(irq, ...);

```

007-4520-007

## **Direct Memory Access Addresses (DMA)**

DMA addresses (bus addresses) on Altix system are either 64 bits or 32 its, nothing in-between. Requests for DMA addresses between 33 and 63 bits are given 32 bits DMA addresses.

Device drivers cannot use legacy macros, such as the following:

```

bus_to_virt()

virt_to_bus()

```

Before calling any of the DMA mapping routines, a device driver should query the system for the DMA address size that the platform supports, using the following:

```

pci_dma_supported()

```

By default, the dma\_mask is set by the Linux operating system to be <code>Oxffffffff</code>, which means 32 bits.

On an Altix system, there no calls to convert addresses from bus-to-virtual or virtual-to-bus. If the driver requires the corresponding virtual address of a bus address, it should save the virtual address.

Linux provides the following routines for mapping Virtual Address to DMA address:

```

pci_alloc_consistent()

pci_free_consistent()

pci_map_single()

pci_unmap_single()

pci_map_sg()

pci_unmap_sg()

pci_unmap_sg()

pci_dma_sync_single()

pci_dma_sync_sg()

```

See linux/Documentation/DMA-mapping.txt for more details.

#### Posted PIO write Calls

For performance reasons, PIO write calls are posted. That is, on return from a PIO write call for example,  $\mathtt{outb}(\mathtt{X})$ , an Altix system does not guarantee that the PIO has arrived and been received by the designated device. To ensure that a PIO write has actually been delivered and received by the designated device, device drivers are required to perform a PIO read to a safe register on the device, for example reading the vendor's identification, and so on:

```

outb(XX);

outb(XX);

inb(safe register address);

```

**Note:** IO writes are delivered as soon as possible. In a ccNUMA architecture like used in an Altix system, if the system is very busy, a PIO write can be buffered by the IO chipsets.

The same rules apply to PIOs using the readb() family of macros.

For more information on synchronization issues regarding PIOs and memory references, see the *Linux Device Drivers Guide*.

007–4520–007

# **Architecture**

This chapter gives an overview of system components and the management of physical and virtual memory in SGI Altix series systems, which are based on the Itanium Processor Family (IPF) of processors. This chapter also provides background information to help you understand the limitations and special conventions used by some kernel functions.

The following main topics are covered in this chapter:

- "System Components" on page 13

- "System Memory Address Space" on page 20

- "Memory Access" on page 31

# **System Components**

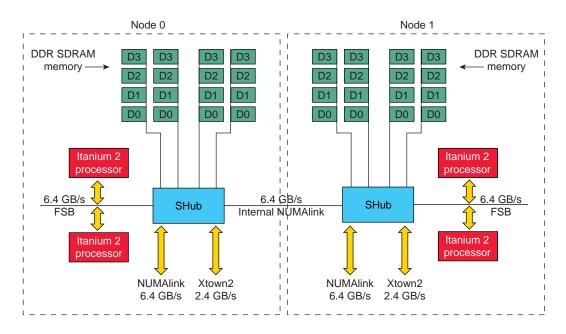

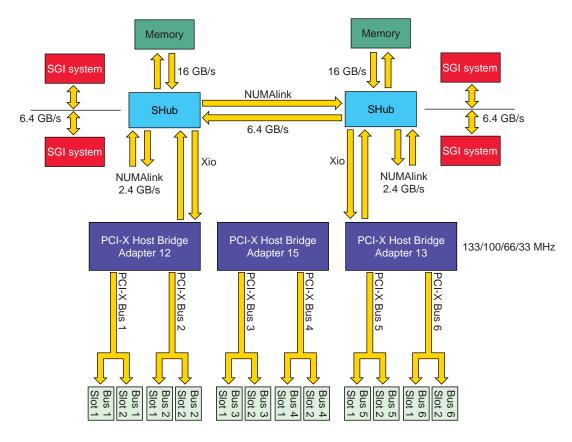

The SGI Altix servers are a family of multiprocessor distributed shared memory (DSM) computer systems. The SGI Altix systems use a global-address-space cache-coherent multiprocessor that can scale up to 512 processors in a cache-coherent domain. The processors are housed in a 3-U high brick called the SC-brick. The SC-brick contains two processor nodes. A processor node consists of two processors, each with 1.5- or 3-MB on-chip, private tertiary (L3) cache, connected to the scalable hub (SHub) ASIC via the front side bus (FSB). The SHub ASIC acts as a crossbar between the processors, local SDRAM memory, the network interface, and the I/O interface. Each processor node is interconnected by a NUMAlink 4 channel. The modularity of the DSM approach combines the advantages of low entry-level cost with global scalability in processors, memory, and I/O. The SGI Altix systems are based on the Intel Itanium 2 processor. The Intel Itanium 2 processor is a 64-bit processor that is initially offered at 900 MHz clock speed with a 1.5 MB L3 cache size.

007–4520–007

The SGI Altix has a PCI-X-based I/O system. (For more details on PCI-X devices, see Chapter 3, "PCI-X Device Attachment" on page 37). The I/O components are housed in an I/O brick. Following are the two types of I/O bricks:

IX-brick An IX-brick consists of six PCI-X buses. One slot is

preloaded with the BaseIO card, plus a drive module containing a DVD-ROM and one or two system disks.

PX-brick A PX-brick consists of six PCI-X buses, each with two

PCI-X slots.

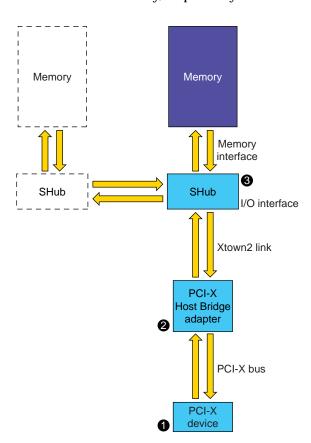

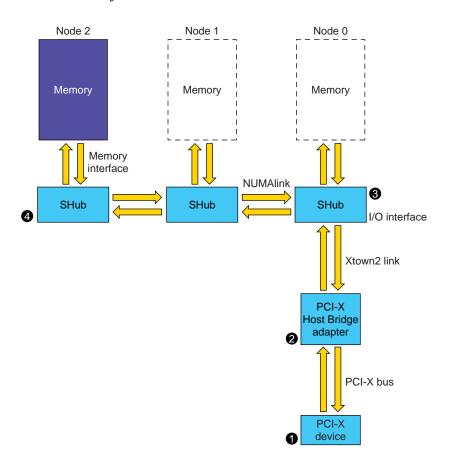

Figure 2-1 on page 15, shows the links between the various bricks of the SGI Altix system.

Figure 2-1 Links Between Bricks

The following sections provide additional information of the various system bricks. These sections describe the following system components:

- Compute/processor node (SC-brick)

- PCI-X with BaseIO (IX-brick)

- PCI-X with expansion (PX-brick)

007–4520–007

### Compute/Processor Node (SC-brick)

The SC-brick is a 3U (4.5"), 1U==1.5", rackmountable enclosure that contains the following components:

- Two processor nodes, each containing two 64-bit processors with 1.5- or 3-MB secondary caches.

- Two SHub chipsets.

- Sixteen DIMM slots per SHub; one or two memory banks per four DIMMs.

- · Node electronics.

- One L1 controller.

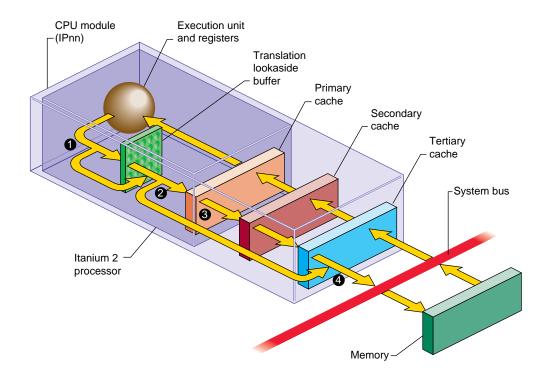

The node electronics, L1 controller, and power regulators are contained on a single half-panel power board (PCB). The two SHubs, four processors, and processor power pods are housed on separate half-panel boards. Four memory daughtercards house the memory DIMMs. Each daughtercard supports eight memory DIMMs. Figure 2-2 on page 17, shows the block diagram of an SC-brick.

**Note:** All transfer rates in Figure 2-2 on page 17, are peak rates.

The \$ in Figure 2-2 on page 17, means "cache."

Figure 2-2 SC-brick Block Diagram

The SC-brick has the following features:

- Two 64-bit processors

- Contains one 1.5- or 3-MB secondary cache per processor (integrated within the processor)

- Configurable from 2.0 GB to 16 GB of main memory (minimum 8 DIMMs)

- Contains two 6.4-GB/s (each direction) NUMAlink channels

- Contains two 2.4-GB/s (each direction) Xtown2 channels

- Contains one connection port to the L2 controller

- · Contains one DB9 console port

007–4520–007

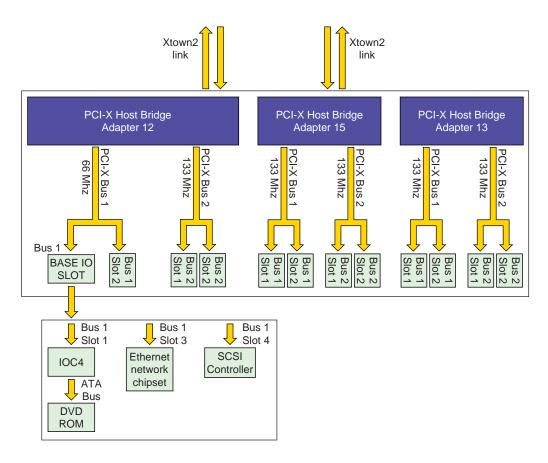

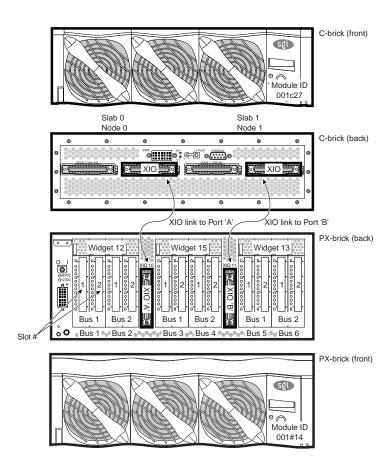

# PCI-X with BaseIO (IX-brick)

The IX-brick is actually a PX-brick with a BaseIO card in PCI-X bus Q, slot Q, plus a drive module. The BaseIO card consists of the following components:

• IOC4 components:

ATA bus connected to DVD-ROM NVRAM Real-time clock Real-time input/output ports Serial ports PS/2 keyboard and mouse ports

- Ethernet network chipset

- · SCSI controller

Figure 2-3 on page 19, shows an IX-brick.

Figure 2-3 IX-brick (PX-brick with BaseIO Card)

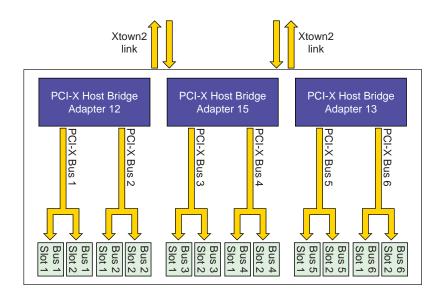

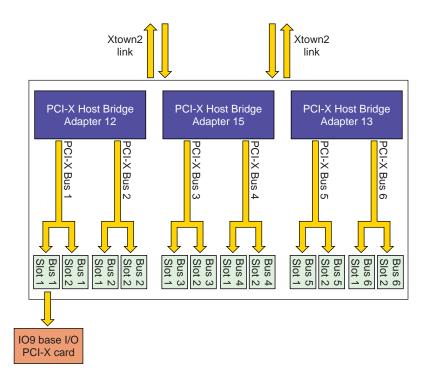

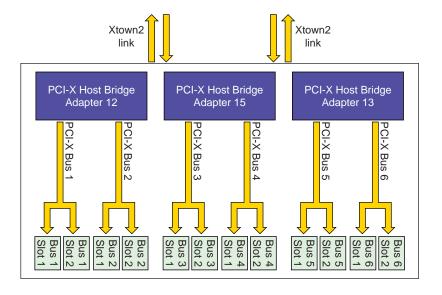

## **PCI-X** with Expansion (PX-brick)

The PX-brick contains six PCI-X buses with two slots per bus to make a total of 12 PCI-X slots. PX-bricks can be connected to the system via two Xtown2 links. The PX-brick PCI-X expansion is shown in Figure 2-4 on page 20.

007–4520–007

Figure 2-4 PX-brick - PCI-X Expansion Brick

# **System Memory Address Space**

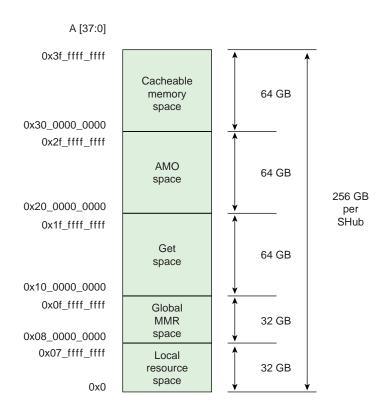

SGI Altix systems support 64-bit mode addressing. This section refers to the 64-bit address spaces provided by the SGI Altix system microprocessor (see Figure 2-8 on page 27). This architecture uses addresses that are 64-bit unsigned integers from 0x0000 0000 0000 0000 to 0xFFFF FFFF FFFF. This is an immense span of numbers—if it were drawn to a scale of 1 millimeter per terabyte, the drawing would be 16.8 kilometers long (just over 10 miles).

The following types of space are described in this section:

- Physical address

- Global Memory mapped register (MMR)

- Atomic memory operation (AMO)

- Cacheable memory

- · SHub physical address map

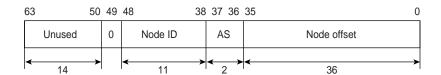

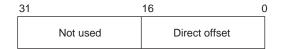

# **Physical Address Space**

This section provides physical address space information that is normally used by device drivers. SGI Altix systems support 50-bit physical addressing, as shown in Figure 2-5 on page 21.

Figure 2-5 Address Decoding for Physical Memory Access

Fields in Figure 2-5 on page 21, are defined as follows:

| Bits   | Description                                                                                                                                                                                                   |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:50  | Unused and reserved for future use. The value of these bits should always be zero. This leaves 512 terabytes of addressing for SGI Altix systems implemented with SHub.                                       |

| 49:38  | Node ID bits. SGI Altix systems implemented with SHub support up to 1024 processor nodes (2048 CPUs per system). Bit 38 indicates the node type. A value of 0 indicates a processor node. Bit 49 is always 0. |

| 37: 36 | Address space (AS). Each SHub is allocated 256 GB of physical address space. Bits 37:36 divide the 256 GB into four 64-GB spaces, as follows:                                                                 |

| Bits [37:36] | Description                               |

|--------------|-------------------------------------------|

| 00           | Local resource space and global MMR space |

| 01           | GET space                                 |

| 10           | AMO space                                 |

| 11           | Cacheable memory space                    |

The AS bits are analogous to the uncached attribute bits of the SGI Origin series systems; however, since Itanium 2 processors do not support uncached attribute bits in the translation lookaside buffer (TLB), physical address bits are used to perform the equivalent function.

Node offset. These bits point to a specific byte location within one of the four 64-GB spaces of the SHub. When the value of bits 37:36 is 0b00, the 64-GB local resource space and global MMR space is really split into two 32-GB regions: 32 GB of local resource space and 32 GB of global MMR space. Bit 35 selects between these two regions. When the value of bits 37:35 is 0b000, the request targets the local resource space. When the value of bits 37:35 is 0b001, the request targets the global MMR space.

The following sections describe global MMR space, AMO space, and cacheable memory space.

#### **Global MMR Space**

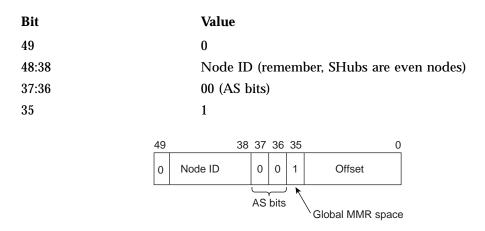

A node's global memory mapped register (MMR) space provides all processor nodes in the system with access to a node's MMRs (see Figure 2-6 on page 23). Notice the position of the global MMR space in the physical address map shown in Figure 2-8 on page 27. Following are the values of the bits for global MMR space:

22 007–4520–007

35:0

Figure 2-6 Bit Values for Global MMR Space

**Note:** Programmable I/O addresses reside in this space (for example, SHub systems, registers set, PCI configuration space, PCI I/O and memory space, I/O brick registers, and so on).

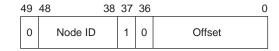

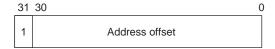

#### **AMO Space**

When the address space (AS) bits are set to 10, the reference is to atomic memory operation (AMO) space. An AMO read operation (AMOR) or AMO write operation (AMOW) request is issued to the SHub that is identified by the number in the node ID (see Figure 2-7 on page 24). Notice the position of the AMO space in the physical address map shown in Figure 2-8 on page 27. The node offset bits specify a 36-bit offset within the SHub address space, as follows:

| Bit   | Value                                    |

|-------|------------------------------------------|

| 49    | 0                                        |

| 48:38 | Node ID (remember, SHubs are even nodes) |

| 37:36 | 10                                       |

| 35:0  | Node offset                              |

Figure 2-7 Bit Values for AMO Space

A number of fetch-and-op style AMOs are supported to optimize common synchronization primitives such as locks, tickets, and barriers. These AMOs operate on a read-modify-write basis. AMOs are defined only for word and doubleword data sizes and are performed using uncached loads and stores to the AMO address space. In addition, operations are allowed only on the first doubleword of each 64-byte block (half cache line) in memory. The AMO variable can be accessed either as one 64-bit AMO variable or as two 32-bit AMO variables.

In the AMO address space, bits 5:3 of the node offset (the three address bits above the doubleword offset) determine the type of AMO to perform.

The following AMO read operations are supported:

Fetch Simple uncached read of the location.

Fetch and Increment The location's current value is returned and then the

location's value is incremented. This operation is

followed by a write operation.

location's value is decremented. This operation is

followed by a write operation.

Fetch and Clear The location's current value is returned and then the

location's value is cleared. This operation is followed

by a write operation.

The following AMO write operations are supported:

Initialize Simple uncached write of the location.

Increment The location's value is incremented.

Decrement The location's value is decremented.

Logical AND Stored data is logically AND'd with the location's

current value.

24 007-4520-007

Logical OR

Stored data is logically OR'd with the location's current value

#### **Cacheable Memory Space**

When the AS bits are set to 11, the reference is to cacheable memory space. A memory request is issued to the SHub that is identified by the number in the node ID. The node offset bits specify a 36-bit offset within the SHub address space. UC, WB, and WC attributes are supported for cacheable memory space. Notice the position of the cacheable memory space in the physical address map shown in Figure 2-8 on page 27. The 50-bit physical address has a 36-bit offset within the SHub address space, as follows:

| Bit   | Value                                    |

|-------|------------------------------------------|

| 49    | 0                                        |

| 48:38 | Node ID (remember, SHubs are even nodes) |

| 37:36 | 11 (AS bits)                             |

| 35:0  | Node offset                              |

Note: Direct memory access (DMA) addresses reside in cacheable memory space.

#### Cache Use

The primary, secondary, and tertiary caches shown in Figure 2-10 on page 32, are essential to CPU performance. There is an order of magnitude difference in the speed of access between cache memory and main memory. Execution speed remains high only as long as a very high proportion of memory accesses are satisfied from the primary, secondary, or tertiary cache.

The use of caches means that there are often multiple copies of data: a copy in main memory, a copy in the secondary cache (when one is used), and a copy in the primary cache. Moreover, a multiprocessor system has multiple CPU modules like the one shown in Figure 2-10 on page 32, and there can be copies of the same data in the cache of each CPU.

007–4520–007

#### **Cache Coherency**

The problem of *cache coherency* is to ensure that all cache copies of data are true reflections of the data in main memory. Different SGI systems use different hardware designs to achieve cache coherency.

Multiprocessor systems have more complex cache coherency protection because it is possible to have data in multiple caches. In an SGI Altix multiprocessor system, the hardware ensures that cache coherency is maintained under all conditions, including DMA input and output, without action by the software.

#### SHub Physical Address Map

Figure 2-8 on page 27 shows the SHub physical address map. On SHub, AMO space and global MMR space must be accessed uncached, and GET space must be accessed cached. Cacheable memory space can be accessed cached or uncached, subject to operating system constraints.

Figure 2-8 SHub Physical Address Map

**Note:** Linux drivers run in virtual mode (TLBs enabled for all addresses) all the time. Therefore, the address space they see depends not only on behavior of the SHub, but also on the TLB mapping conventions of the operating system.

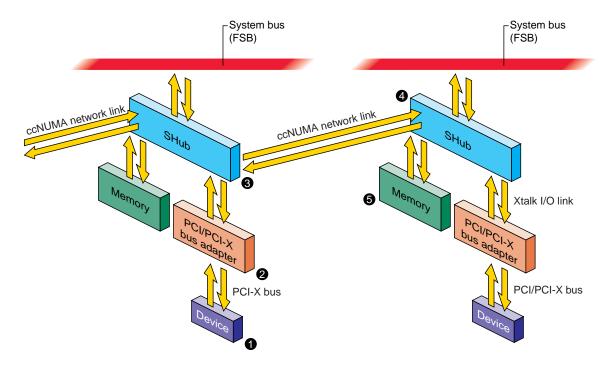

#### **PIO Addresses and DMA Addresses**

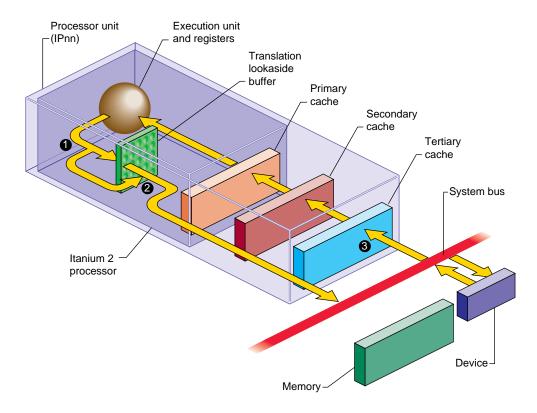

Figure 2-12 on page 35, is too simple for some devices that are attached through a bus adapter. A bus adapter connects a bus of a different type to the system bus, as shown in Figure 2-9 on page 28.

007–4520–007 27

Figure 2-9 Device Access through a Bus Adapter

For example, the PCI/PCI-X bus adapter connects a PCI/PCI-X bus to the Xtalk I/O interface of SHub. Multiple PCI/PCI-X devices can be plugged into the PCI/PCI-X bus and use the bus to read and write. The bus adapter translates the PCI/PCI-X bus protocol into the system Xtalk protocol.

Each PCI/PCI-X bus has address lines that carry the address values used by devices on that PCI/PCI-X bus. These bus addresses are not related to the physical addresses used on the system front side bus (FSB). The issue of bus addressing is made complicated by three facts:

- Bus-master devices independently generate memory-read and memory-write commands that are intended to access system memory.

- The bus adapter can translate addresses between addresses on the bus it manages, and different addresses on the system bus it uses.

• The translation done by the bus adapter can be programmed dynamically (mapped), and can change from one I/O operation to another.

This subject can be simplified by dividing it into two distinct subjects: PIO addressing, used by the CPU to access a device, and DMA addressing, used by a bus master to access memory. These addressing modes need to be treated differently.

#### **PIO Addressing**

Programmable I/O (PIO) is the term for a load or store instruction executed by the CPU that names an I/O device space as its operand. The CPU places a physical address on the system bus. The bus adapter repeats the read or write command on its bus, but not necessarily using the same address bits as the CPU put on the system bus.

One task of a bus adapter is to translate between the physical addresses used on the system bus and the addressing scheme used within the proprietary bus. The address placed on the target bus is not necessarily the same as the address generated by the CPU. The translation is done differently with different bus adapters and in different system models.

With the more sophisticated PCI and PCI-X buses, the translation is dynamic. Both of these buses support bus address spaces that are as large or larger than the physical address space of the system bus. It is impossible to hard-wire a translation of the entire bus address space. Furthermore, SGI Altix architecture provides multiple system buses. For more details, see "Address Spaces Supported" on page 42.

The PCI/PCI-X resource addresses in the pci\_dev structure are PIO mapped addresses that the device driver can use in their existing state.

#### **PIO Addressing Extension**

To use a dynamic PIO address, a device driver can create a software object called a PIO map that represents that portion of bus address space that contains the device registers the driver uses. When the driver wants to use the PIO map, the kernel dynamically sets up a translation from an unused part of physical address space to the needed part of the bus address space. The driver extracts an address from the PIO map and uses it as the base for accessing the device registers. This is an extension that SGI provides.

#### **DMA Addressing**

A bus-master device on the PCI bus can be programmed to perform transfers to or from memory independently and asynchronously. A bus master is programmed using PIOs with a starting bus address and a length. The bus master generates a series of memory-read or memory-write operations to successive addresses. But what bus addresses should it use in order to store into the proper memory addresses?

The bus adapter translates the addresses used on the proprietary bus to corresponding addresses on the system bus. As shown in Figure 2-9 on page 28, the operation of a DMA device is as follows:

- 1. The device places a bus address and data on the PCI or PCI-X bus.

- 2. The bus adapter translates the address to a meaningful physical address, and places that address and the data on the system Xtalk I/O link.

- 3. The memory modules store the data.

The translation of bus virtual to physical addresses is done by the bus adapter and programmed by the kernel. A device driver requests the kernel to set up a dynamic mapping from a designated memory buffer to bus addresses. For more information, see Chapter 9, "PCI-X Direct Memory Access (DMA)" on page 77.

Linux device drivers on SGI Altix systems must use the standard Linux pci\_dma map routines. For more information, see Chapter 9, "PCI-X Direct Memory Access (DMA)" on page 77.

#### **DMA Addressing Extension**

The driver calls kernel functions to establish the range of memory addresses that the bus master device will need to access—typically the address of an I/O buffer. When the driver calls one of the pci\_dma map routines, the kernel sets up the bus adapter hardware to translate between some range of bus addresses and the desired range of memory space. The driver uses PIO to program this bus address into the bus master device registers. SGI software supports 64- and 32-bit DMA addresses. For more information on 64- and 32-bit DMA map addresses, see Chapter 9, "PCI-X Direct Memory Access (DMA)" on page 77.

#### **Linux Kernel and User Virtual Address Management**

The SGI Altix system uses the same virtual memory manager as any IA-64 Linux system with ccNUMA and discontiguous memory support. For more information on

Linux kernel and user virtual address management, see IA-64 Linux Kernel Design and Implementation.

# **Memory Access**

The following sections describe CPU and device access to memory.

### CPU Access to Memory or I/O Address Space

Each SGI computer system has one or more CPU modules and one or more I/O modules. A CPU reads data from memory or a device by placing an address on a system bus and receiving data back from the addressed memory or device. An address can be translated more than once as it passes through multiple layers of I/O chipsets and bus adapters. Access to memory can also pass through multiple levels of cache.

# **CPU Access to Memory**

The CPU generates the address of data that it needs—the address of an instruction to fetch, or the address of an operand of an instruction. It requests the data through a mechanism that is depicted in simplified form in Figure 2-10 on page 32.

007-4520-007

Figure 2-10 CPU Access to Memory

#### The process is as follows:

- 1. The address of the needed data is formed in the processor execution or instruction-fetch unit. Most addresses are then mapped from virtual to real through the translation lookaside buffer (TLB). On Itanium 2 processors, all addresses go through the TLBs if TLBs are enabled. With some very small exceptions, TLBs are always enabled.

- 2. Most addresses are presented to the L1 cache, a cache in the processor chip. If a copy of the data with that address is found, it is returned immediately. Certain address ranges are never cached; these addresses pass directly to the bus.

- 3. If the L1 cache does not contain the data, the address is presented to the L2 cache. If it contains a copy of the data, the data is returned immediately. The size and the architecture of the secondary cache differ from one CPU model to another.

4. If L2 does not contain the data, the address is presented to the L3 cache. The address is placed on the system bus. The memory module that recognizes the address places the data on the bus.

The process in Figure 2-10 on page 32 is correct for an SGI Altix system when the addressed data is in the local node.

**Note:** When the address applies to memory in another node, the address passes out through the connection fabric to a memory module in another node, from which the data is returned.

### CPU Access to I/O Address Space – Programmable I/O (PIO)

The CPU accesses a device register using *programmable I/O* (PIO), a process illustrated in Figure 2-11 on page 34. Access to device registers is always uncached. It is not affected by considerations of memory cache coherency in any system (see "Cache Use" on page 25).

Figure 2-11 CPU Access to Device Registers (Programmable I/O)

The process is as follows:

- 1. The address of the device is formed in the execution unit. It is not usually an address that is mapped by the TLB.

- 2. A device address, after mapping if necessary, always falls in one of the ranges that is not cached, so it passes directly to the system bus.

- 3. The device or system component (such as SHub) recognizes its physical address and responds with data.

The PIO process shown in Figure 2-11 on page 34, is correct for an SGI Altix system when the addressed device is attached to the same node. When the device is attached to a different node, the address passes through the connection fabric to that node, and the data returns the same way.

### **Device Access to System Physical Memory Space – Direct Memory Access**

Some devices can perform *direct memory access* (DMA), in which the device itself, not the CPU, reads or writes data into memory. A device that can perform DMA is called a *bus master* because it independently generates a sequence of bus accesses without help from the CPU.

To read or write a sequence of memory addresses, the bus master has to be told the proper physical address (bus address) range to use. This is done by using PIO to store a bus address and length into the device's registers from the CPU. When the device has the DMA information, it can access memory through the system bus as shown in Figure 2-12 on page 35.

Figure 2-12 Device Access to Memory

The process is as follows:

1. The device makes a request on the PCI/PCI-X bus.

007–4520–007 35

- 2. The PCI/PCI-X bus adapter translates the PCI/PCI-X bus request and generates a request to the I/O chipset (SHub).

- 3. The local SHub forwards the request to the requested memory controllers (local or remote).

- 4. The memory module stores the data.

In an SGI Altix system, the device and the memory module can be in different nodes, with address and data passing through the connection fabric (NUMAlink) between nodes.

When a device is programmed with an invalid physical address, the result is a bus error interrupt. The interrupt occurs on some CPU that is enabled for bus error interrupts. These interrupts are not simple to process for two reasons. First, the CPU that receives the interrupt is not necessarily the CPU from which the DMA operation was programmed. Second, the bus error can occur a long time after the operation was initiated.

# **PCI-X Device Attachment**

The peripheral component interconnect (PCI) bus, initially designed at Intel, is standardized by the PCI special interest group, a nonprofit consortium of vendors. PCI-X is the successor to PCI. Both PCI and PCI-X devices can be used on a PCI-X bus. SGI Altix system architecture supports the PCI-X bus. All peripheral devices on SGI Altix systems are connected via PCI-X buses. The PCI-X bus is designed as a high-performance local bus to connect peripherals to memory and a microprocessor.

This chapter describes PCI-X implementation in larger architectures such as the SGI Altix systems.

For more information about PCI-X system architecture, see PCI-X System Architecture.

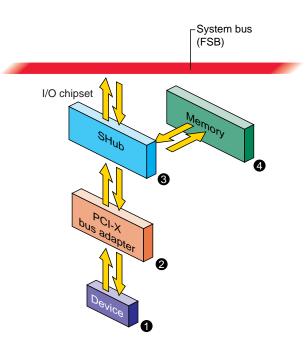

# **PX-brick with BaselO (IX-brick)**

The PX-brick with BaseIO is a Crosstalk-to-PCI-X based I/O subsystem. It has two 1200-MB/s Xtown2 connectors and one or two of them can be used to connect to SC-bricks. There are 12 PCI slots that are configured on 6 buses and 2 hard disk bays that support SCSI disk drives and a DVD-ROM. The DVD-ROM is not SCSI; it is connected through parallel ATA. For peak bandwidth values, see Table 3-1 on page 37. Figure 3-1 on page 38, depicts the PX-brick with BaseIO.

Table 3-1 Bandwidth Characteristics of the IX-brick

| Description                                        | Peak Bandwidth                                                |

|----------------------------------------------------|---------------------------------------------------------------|

| Xtown2 ports — A and B                             | 1200 MB/s                                                     |

| PCI-X bus frequency: 33 MHz 66 MHz 100 MHz 133 MHz | 64-bit mode:<br>256 MB/s<br>512 MB/s<br>800 MB/s<br>1024 MB/s |

Note 1: PCI-X mode achieves a higher percentage of theoretical peak versus PCI mode.

007–4520–007 37

Note 2: To run the bus at 133 MHz requires only one card on that bus and it must be a 133-MHz capable card.

Note3: The IO9 is a 66-MHz PCI card, so bus 1 runs at 66 MHz PCI in the IX-brick.

Figure 3-1 PX-brick with BaseIO

# **PX-brick Expansion**

The PX-brick has two 1200-MB/s Xtown2 ports that connect SC-bricks. There are 12 PCI slots that are configured on 6 buses. For peak and sustained bandwidth values, see Table 3-2 on page 39. Figure 3-2 on page 39, depicts a PX-brick PCI-X expansion.

**Table 3-2** Bandwidth Characteristics of the PX-brick

| Peak Bandwidth |

|----------------|

| 1200 MB/s      |

| 64-bit mode:   |

| 256 MB/s       |

| 512 MB/s       |

| 800 MB/s       |

| 1024 MB/s      |

|                |

Note 1: PCI-X mode achieves a higher percentage of theoretical peak versus PCI mode.

Note 2: To run the bus at 133 MHz requires only one card on that bus and it must be a 133-MHz capable card.

Figure 3-2 PX-brick PCI-X Expansion

# **PCI-X Implementation**

In SGI Altix systems, the PCI-X adapter connects to the high-speed XIO bus. This bridge joins the PCI-X bus into the connection fabric, so that any PCI-X bus can be addressed from any module, and any PCI-X bus can access memory that is physically located in any module, as shown in Figure 3-3 on page 40.

Figure 3-3 PCI-X Implementation

### **Latency and Operation Order**

In SGI Altix systems, the multimedia features have substantial local resources, so contention with multimedia for the use of main memory is lower. However, these

systems also have multiple CPUs and multiple layers of address translation, and these factors can introduce latencies in PCI-X transactions.

It is important to understand that there is **no guaranteed order of execution between separate PCI-X transactions in these systems**. There can be multiple hardware layers between the CPU, memory, and the device. One or more data transactions can be "in flight" for durations that are significant. For example, suppose that a PCI-X bus-master device completes the last transfer of a DMA write of data to memory, and then executes a DMA write to update a status flag elsewhere in memory.

Under circumstances that are unusual but not impossible, the status in memory can be updated and acted upon by software, while the data transaction is still "in flight" and has not completely arrived in memory. The same can be true of a programmable I/O (PIO) read that polls the device. It can return "complete" status from the device while data sent by DMA has yet to reach memory.

Ordering is guaranteed when interrupts are used. An interrupt handler is not executed until all writes initiated by the interrupting device have completed.

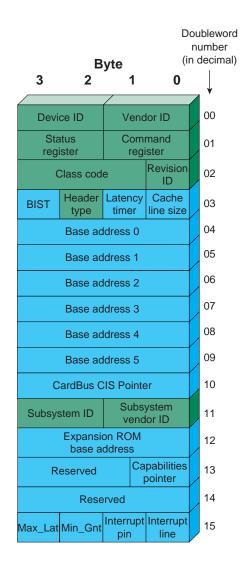

## **Configuration Register Initialization**

When the Linux kernel scans the PCI-X buses on an SGI Altix system and finds an active device, it initializes the device configuration registers as follows:

| Command register | The enabling bits for I/O access, memory access, and master are set to 1. Other bits, such as memory write, invalidate, and fast back-to-back are left at 0.                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache line size  | Set at 0x20 (32, 32-bit words, or 128 bytes).                                                                                                                                                                                                                            |

| Latency timer    | Setting depends on bus speed and the device's Min_Gnt (minimum grant) register. If the device's Min_Gnt value is 0, the latency timer is set to 1 microsecond. Otherwise, it is set to (min_gnt_mult * Min_Gnt). Values for min_gnt_multdepend on bus speed, as follows: |

| <pre>min_gnt_mult Value</pre> |

|-------------------------------|

| 32                            |

| 24                            |

| 16                            |

| 8                             |

|                               |

Base address registers

Each register that requests PCI memory or PCI I/O address space is programmed with a starting address.

Note: This address is valid only for this PCI-X bus.

When attaching a device, the device driver can set any other configuration parameters.

**Caution:** If the driver changes the contents of a base address register, the results are unpredictable. Do not do this.

## **Unsupported PCI-X Signals**

The following optional signal lines are not supported:

- The LOCK# signal is ignored; atomic access to memory is not supported.

- The cache-snoop signals SBO# and SDONE are ignored. Cache coherency is ensured by the PCI-X adapter and the memory architecture, with assistance by the driver.

#### **Address Spaces Supported**

In SGI Altix systems, addresses are translated not once but at least twice and sometimes more often between the CPU and the device, or between the device and memory. Also, some of the logic for features, such as prefetching and byte-swapping, is controlled by the use of high-order address bits. There is no simple function on a physical memory address that yields a PCI-X bus address (nor vice-versa). The device driver must use the PIO addresses presented in the pci-dev structure. For more information, see Chapter 7, "PCI-X I/O and Memory Resources" on page 61.

It is also necessary for the device driver to call the relevant DMA mapping routines for DMA addresses (PCI-X bus addresses). For more information, see Chapter 9, "PCI-X Direct Memory Access (DMA)" on page 77.

#### 64-bit Address and Data Support

SGI Altix systems support 64-bit data transactions. Use of 64-bit data transactions results in best performance. The PCI-X adapter accepts 64-bit addresses produced by a bus-master device. The PCI-X adapter does not generate 64-bit addresses itself.

42 007-4520-007