# sgi

REACT<sup>™</sup> Real-Time for Linux<sup>®</sup> Programmer Guide

#### COPYRIGHT

© 2005–2008, 2010–2015 Silicon Graphics International Corp. All rights reserved; provided portions may be copyright in third parties, as indicated elsewhere herein. No permission is granted to copy, distribute, or create derivative works from the contents of this electronic documentation in any manner, in whole or in part, without the prior written permission of SGI.

#### LIMITED RIGHTS LEGEND

The software described in this document is "commercial computer software" provided with restricted rights (except as to included open/free source) as specified in the FAR 52.227-19 and/or the DFAR 227.7202, or successive sections. Use beyond license provisions is a violation of worldwide intellectual property laws, treaties and conventions. This document is provided with limited rights as defined in 52.227-14.

#### TRADEMARKS AND ATTRIBUTIONS

Altix, REACT, SGI, UV, the SGI cube, the SGI logo are trademarks or registered trademarks of Silicon Graphics International Corp. or its subsidiaries in the United States and other countries.

IBM is a registered trademark of IBM Corporation. Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries. Linux is a registered trademark of Linus Torvalds in several countries. LSI Logic is a registered trademark of LSI Corporation. Novell and SUSE are registered trademarks of Novell, Inc. in the United States and other countries. Red Hat and all Red Hat-based trademarks are trademarks or registered trademarks of Red Hat, Inc. in the United States and other countries. All other trademarks mentioned herein are the property of their respective owners.

# New Features in this Guide

This version includes the following:

- Documentation in support of the SGI PCIE-RT real-time interrupt card. See "Example: SGI PCIE-RT Real-Time Interrupt Card" on page 32.

- Revised instructions to use the cpu\_shield library routine. See "cpu\_shield" on page 136.

# **Record of Revision**

| Version | Description                                                                    |

|---------|--------------------------------------------------------------------------------|

| 001     | February 2005<br>Original publication to support REACT real-time for Linux 4.0 |

| 002     | July 2005<br>Revision to support REACT real-time for Linux 4.2                 |

| 003     | December 2005<br>Revision to support REACT real-time for Linux 4.3             |

| 004     | July 2006<br>Revision to support REACT real-time for Linux 5.0                 |

| 005     | February 2007<br>Revision to support REACT real-time for Linux 5.1             |

| 006     | June 2007<br>Revision to support REACT real-time for Linux 5.2                 |

| 007     | September 2007<br>Revision to support REACT real-time for Linux 5.3            |

| 008     | December 2007<br>Revision to support REACT real-time for Linux 5.4             |

| 009     | March 2008<br>Revision to support REACT real-time for Linux 5.5                |

| 010     | June 2008<br>Revision to support REACT real-time for Linux 6.0                 |

| 011     | September 2008<br>Revision to support REACT real-time for Linux 6.1            |

| 012     | January 2010<br>Revision to support REACT real-time for Linux 7.0              |

| 013 | May 2010                                                                                                                 |

|-----|--------------------------------------------------------------------------------------------------------------------------|

|     | Revision to support REACT real-time for Linux 7.1 (part of the SGI ProPack 7.1 release)                                  |

| 014 | October 2010<br>Revision to support SGI REACT 1.0 (a new separate release, and a<br>member of the SGI Performance Suite) |

| 015 | January 2011<br>Revision to support SGI REACT 1.1                                                                        |

| 016 | October 2011<br>Revision to support SGI REACT 1.3                                                                        |

| 017 | April 2012<br>Revision to support SGI REACT 1.4                                                                          |

| 018 | October 2012<br>Revision to support SGI REACT 1.5                                                                        |

| 019 | October 2013<br>Revision to support SGI REACT 1.7                                                                        |

| 020 | March 2014<br>Revision to support SGI REACT 1.8                                                                          |

| 021 | October 2014<br>Revision to support SGI REACT 1.9                                                                        |

| 022 | April 2015<br>Revision to support SGI REACT 1.10                                                                         |

| About This Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xxiii |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Audience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xxiii |

| What This Guide Contains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xxiii |

| Related Publications and Sites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xxv   |

| Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xxvi  |

| Obtaining Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xxvi  |

| Reader Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xxvii |

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1     |

| Real-Time Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1     |

| Real-Time Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2     |

| Simulators and Stimulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2     |

| Aircraft Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3     |

| Ground Vehicle Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3     |

| Plant Control Simulators    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .     | 3     |

| Virtual Reality Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4     |

| Hardware-in-the-Loop Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4     |

| Control Law Processor Stimulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4     |

| Wave Tank Stimulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5     |

| Data Collection Systems    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    < | 5     |

| Process Control Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6     |

| <b>REACT</b> <sup><math>^{\text{TM}}</math></sup> Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6     |

| REACT Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7     |

| REACT RPMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8     |

| 2. Linux and REACT Support for Real-Time Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9     |

| 007–4746–022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | vii   |

| Kernel Facilities                                                                                                                                                                                                                                                                     |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   | •               | •                                     |                  |                  |             | 9                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------|-------------------|------------------|-------------------------|-------------------|---------------|---------------|-------------------------|---------------|---------------|-------------|-------------------|-----------------|---------------------------------------|------------------|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|

| Special Scheduling Disciplines                                                                                                                                                                                                                                                        |   | •                                     |                   | •                | •                       | •                 |               | •             | •                       | •             |               |             |                   | •               | •                                     | •                | •                | •           | 9                                                                                                                                  |

| Virtual Memory Locking                                                                                                                                                                                                                                                                |   |                                       |                   | •                | •                       |                   |               |               |                         | •             |               |             |                   | •               | •                                     |                  |                  |             | 10                                                                                                                                 |

| Processes Mapping and CPUs .                                                                                                                                                                                                                                                          |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 | •                                     |                  |                  |             | 10                                                                                                                                 |

| Interrupt Distribution Control .                                                                                                                                                                                                                                                      |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 | •                                     |                  |                  |             | 11                                                                                                                                 |

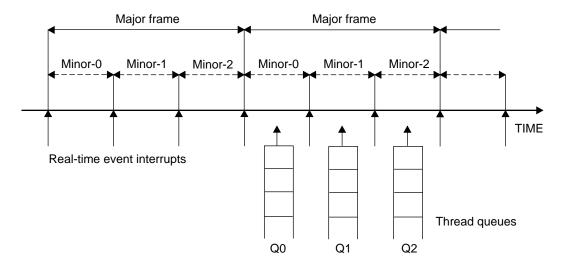

| Frame Scheduler                                                                                                                                                                                                                                                                       |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 |                                       |                  |                  |             | 11                                                                                                                                 |

| Real-Time Clocks and Timers .                                                                                                                                                                                                                                                         |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 |                                       |                  |                  |             | 12                                                                                                                                 |

| Determining the Clock Source .                                                                                                                                                                                                                                                        | • | •                                     |                   |                  |                         |                   |               |               |                         |               |               |             | •                 |                 | •                                     |                  |                  |             | 12                                                                                                                                 |

| Real-Time Clocks                                                                                                                                                                                                                                                                      |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 | •                                     |                  |                  |             | 13                                                                                                                                 |

| Direct RTC Access                                                                                                                                                                                                                                                                     |   |                                       |                   | •                | •                       |                   |               |               |                         |               |               |             |                   | •               | •                                     |                  |                  |             | 14                                                                                                                                 |

| Interchassis Communication                                                                                                                                                                                                                                                            |   | •                                     |                   | •                | •                       | •                 |               |               | •                       | •             |               |             | •                 | •               | •                                     |                  |                  | •           | 14                                                                                                                                 |

| Socket Programming                                                                                                                                                                                                                                                                    | • | •                                     | •                 | •                | •                       | •                 | •             | •             | •                       | •             | •             | •           | •                 | •               | •                                     | •                | •                | •           | 14                                                                                                                                 |

| Message-Passing Interface (MPI)                                                                                                                                                                                                                                                       | • | •                                     |                   | •                | •                       |                   |               |               | •                       |               |               |             | •                 | •               | •                                     |                  |                  |             | 15                                                                                                                                 |

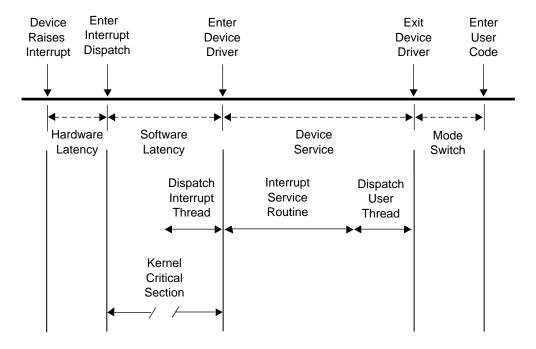

| 3. External Interrupts                                                                                                                                                                                                                                                                |   | •                                     | •                 | •                |                         |                   | •             | •             | •                       | •             | •             | •           | •                 | •               | •                                     | •                | •                | •           | 17                                                                                                                                 |

|                                                                                                                                                                                                                                                                                       |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 |                                       |                  |                  |             | 17                                                                                                                                 |

| Abstraction Layer                                                                                                                                                                                                                                                                     | • | •                                     | •                 | •                | •                       | •                 |               |               |                         |               |               | •           | •                 | •               | •                                     | •                | •                | •           |                                                                                                                                    |

| Abstraction Layer                                                                                                                                                                                                                                                                     |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 |                                       |                  | •                | •           | 18                                                                                                                                 |

| 5                                                                                                                                                                                                                                                                                     |   |                                       |                   |                  |                         | •                 |               |               |                         |               | •             |             | •                 | •               | •                                     |                  |                  |             |                                                                                                                                    |

| sysfs Attribute Files                                                                                                                                                                                                                                                                 | • | •                                     | •                 |                  |                         | •                 |               | •             | •                       |               | •             | •           | •                 | •               |                                       |                  |                  |             | 18                                                                                                                                 |

| sysfs Attribute Files<br>The /dev/extint#Device .                                                                                                                                                                                                                                     |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   | •               |                                       |                  |                  |             | 18<br>20                                                                                                                           |

| sysfs Attribute Files<br>The /dev/extint#Device .<br>Counting Interrupts                                                                                                                                                                                                              |   |                                       |                   |                  |                         |                   |               |               | •                       |               |               |             |                   |                 |                                       |                  |                  |             | 18<br>20<br>20                                                                                                                     |

| sysfs Attribute Files<br>The /dev/extint#Device .<br>Counting Interrupts<br>Waiting for Interrupts                                                                                                                                                                                    |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             |                   |                 |                                       |                  |                  |             | 18<br>20<br>20<br>20                                                                                                               |

| sysfs Attribute Files<br>The /dev/extint# Device .<br>Counting Interrupts<br>Waiting for Interrupts<br>Exclusively Accessing a Device                                                                                                                                                 |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             | · · · ·           |                 |                                       |                  |                  |             | 18<br>20<br>20<br>20<br>20                                                                                                         |

| sysfs Attribute Files<br>The /dev/extint# Device .<br>Counting Interrupts<br>Waiting for Interrupts<br>Exclusively Accessing a Device<br>Low-Level Driver Interface .                                                                                                                 |   | ·<br>·<br>·                           |                   |                  | ·<br>·<br>·             | · · · · · · ·     | · · · · · ·   |               |                         | · · · · · ·   | · · · · · ·   | • • • •     | · · · · ·         |                 | ·<br>·<br>·                           | ·<br>·<br>·      |                  |             | 18<br>20<br>20<br>20<br>20<br>20<br>24                                                                                             |

| sysfs Attribute Files<br>The /dev/extint# Device .<br>Counting Interrupts<br>Waiting for Interrupts<br>Exclusively Accessing a Device<br>Low-Level Driver Interface .<br>Driver Registration                                                                                          |   | · · · · · · ·                         | · · · · · ·       |                  | · · · · · ·             | · · · · · ·       | • • • •       | • • • • • •   |                         | · · · · · · · | • • • • •     | • • • • •   | · · · · · ·       | • • • •         | ·<br>·<br>·                           | ·<br>·<br>·      |                  |             | 18<br>20<br>20<br>20<br>20<br>20<br>24<br>24                                                                                       |

| sysfs Attribute Files<br>The /dev/extint# Device .<br>Counting Interrupts<br>Waiting for Interrupts<br>Exclusively Accessing a Device<br>Low-Level Driver Interface .<br>Driver Registration<br>Implementation Functions .<br>When an External Interrupt Occ                          |   | · · · · · · · · · · · · · · · · · · · | ·<br>·<br>·<br>·  | ·<br>·<br>·<br>· | · · · · · · ·           | • • • • • •       | • • • • • • • | • • • • • • • | · · · · · · · · ·       | • • • • • •   | • • • • • •   | • • • • • • | · · · · · · · · · | • • • • • •     | · · · · · · · ·                       | · · · · · · · ·  | ·<br>·<br>·<br>· | • • • • • • | <ol> <li>18</li> <li>20</li> <li>20</li> <li>20</li> <li>20</li> <li>24</li> <li>24</li> <li>25</li> </ol>                         |

| sysfs Attribute Files<br>The /dev/extint# Device .<br>Counting Interrupts<br>Waiting for Interrupts<br>Exclusively Accessing a Device<br>Low-Level Driver Interface .<br>Driver Registration<br>Implementation Functions .<br>When an External Interrupt Occ<br>Driver Deregistration |   | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · |                  | · · · · · · · · · · · · | · · · · · · · · · | • • • • • • • | • • • • • • • | · · · · · · · · · · · · | • • • • • •   | • • • • • • • |             | • • • • • • •     | • • • • • •     | · · · · · · · · · · · · · · · · · · · | ·<br>·<br>·<br>· | ·<br>·<br>·<br>· | • • • • • • | <ol> <li>18</li> <li>20</li> <li>20</li> <li>20</li> <li>20</li> <li>24</li> <li>24</li> <li>25</li> <li>29</li> <li>29</li> </ol> |

| sysfs Attribute Files<br>The /dev/extint# Device .<br>Counting Interrupts<br>Waiting for Interrupts<br>Exclusively Accessing a Device<br>Low-Level Driver Interface .<br>Driver Registration<br>Implementation Functions .<br>When an External Interrupt Occ                          |   |                                       |                   |                  |                         |                   |               |               |                         |               |               |             | · · · · · · · · · | • • • • • • • • | ·<br>·<br>·<br>·                      | ·<br>·<br>·<br>· | ·<br>·<br>·<br>· | • • • • • • | <ol> <li>18</li> <li>20</li> <li>20</li> <li>20</li> <li>20</li> <li>24</li> <li>24</li> <li>25</li> <li>29</li> </ol>             |

| Callout Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Callout Registration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                                             |

| Callout Deregistration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                                                                             |

| Low-level Driver Template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                                                                                             |

| Example: SGI PCIE-RT Real-Time Interrupt Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                                                                                             |

| Overview of the PCIE-RT Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                             |

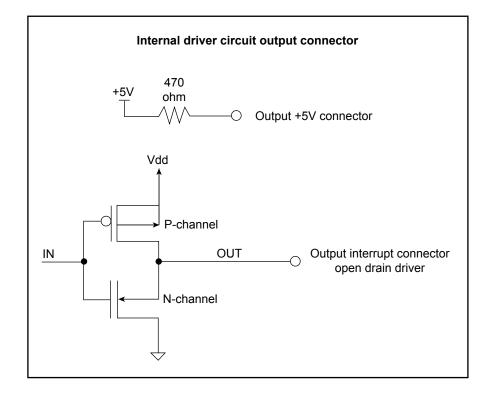

| External Interrupt Output for the PCIE-RT Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                                                             |

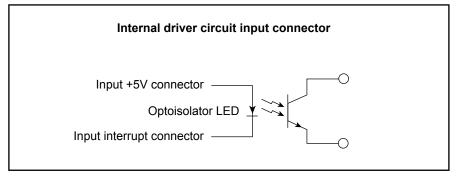

| External Interrupt Ingest for the PCIE-RT Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43                                                                                             |

| Physical Interfaces for the PCIE-RT Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43                                                                                             |

| Example: SGI IOC4 PCI Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                             |

| Multiple Independent Drivers for the IOC4 PCI Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                             |

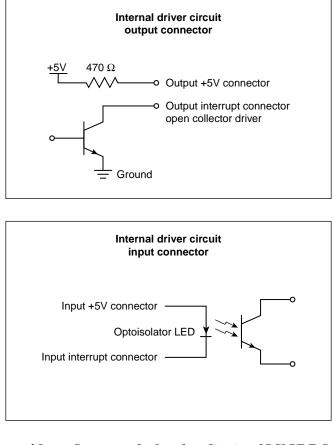

| External Interrupt Output for the IOC4 PCI Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47                                                                                             |

| External Interrupt Ingest for the IOC4 PCI Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49                                                                                             |

| · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                |